# pITX-MX8M-PLUS

User Guide Rev. 1.0

Doc ID: 1822-7820

pITX-MX8M-PLUS – User Guide Rev. 1.0

This page has been intentionally left blank

#### pITX-MX8M-PLUS USER GUIDE

#### Disclaimer

Embedian would like to point out that the information contained in this manual may be subject to alteration, particularly as a result of the constant upgrading of Embedian products. This document does not entail any guarantee on the part of Embedian with respect to technical processes described in the manual or any product characteristics set out in the manual. Embedian assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright or mask work rights to these products and makes no representations or warranties that these products are free from patent, copyright or mask work right infringement unless otherwise specified. Applications that are described in this manual are for illustration purposes only. Embedian makes no representation or warranty that such application will be suitable for the specified use without further testing or modification. Embedian expressly informs the user that this manual only contains a general description of processes and instructions which may not be applicable in every individual case. In cases of doubt, please contact Embedian.

This manual is protected by copyright. All rights are reserved by Embedian. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), without the express written permission of Embedian. Embedian points out that the information contained in this manual is constantly being updated in line with the technical alterations and improvements made by Embedian to the products and thus this manual only reflects the technical status of the products by Embedian at the time of publishing.

Brand and product names are trademarks or registered trademarks of their respective owners.

©2022 by Embedian, Inc.

Embedian, Inc.

9F.-4, 432 Keelung Rd. Sec. 1, XinYi Dist.

Taipei 11051, Taiwan

www.embedian.com

#### Intended Use

THIS DEVICE AND ASSOCIATED SOFTWARE ARE NOT DESIGNED, MANUFACTURED OR INTENDED FOR USE OR RESALE FOR THE OPERATION OF NUCLEAR FACILITIES, THE NAVIGATION, CONTROL OR COMMUNICATION SYSTEMS FOR AIRCRAFT OR OTHER TRANSPORTATION, AIR TRAFFIC CONTROL, LIFE SUPPORT OR LIFE SUSTAINING APPLICATIONS, WEAPONS SYSTEMS, OR ANY OTHER APPLICATION IN A HAZARDOUS ENVIRONMENT, OR REQUIRING FAIL-SAFE PERFORMANCE, OR IN WHICH THE FAILURE OF PRODUCTS COULD LEAD DIRECTLY TO DEATH, PERSONAL INJURY, OR SEVERE PHYSICAL OR ENVIRONMENTAL DAMAGE (COLLECTIVELY, "HIGH RISK APPLICATIONS").

You understand and agree that your use of Embedian devices as a component in High Risk Applications is entirely at your risk. To minimize the risks associated with your products and applications, you should provide adequate design and operating safeguards. You are solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning your products. You are responsible to ensure that your systems (and any Embedian hardware or software components incorporated in your systems) meet all applicable requirements. Unless otherwise stated in the product documentation, the Embedian device is not provided with error-tolerance capabilities and cannot therefore be deemed as being engineered, manufactured or setup to be compliant for implementation or for resale as device in High Risk Applications. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested Embedian products, and other materials) is provided for reference only.

Handling and operation of the product is permitted only for trained personnel within a work place that is access controlled. Please follow the "General Safety Instructions" supplied with the system.

NOTICE

You find the most recent version of the "General Safety Instructions" online in the download area of this product.

# **Revision History**

| Revision | Brief Description of Changes | Date of Issue | Author |

|----------|------------------------------|---------------|--------|

| 1.0      | Initial Issue                | 2022-July-01  | ykl    |

|          |                              |               |        |

|          |                              |               |        |

|          |                              |               |        |

#### Terms and Conditions

Embedian warrants products in accordance with defined regional warranty periods. For more information about warranty compliance and conformity, and the warranty period in your region, visit http://www.embedian.com/index.php?main\_page=terms\_and\_conditions.

Embedian sells products worldwide and declares regional General Terms & Conditions of Sale, and Purchase Order Terms & Conditions. Visit http://www.embedian.com/index.php?main\_page=terms\_and\_conditions.

For contact information, refer to the corporate offices contact information on the last page of this user guide or visit our website CONTACT US.

### **Customer Support**

Find Embedian contacts by visiting: http://www.embedian.com.

#### **Customer Service**

As a trusted technology innovator and global solutions provider, Embedian extends its embedded market strengths into a services portfolio allowing companies to break the barriers of traditional product lifecycles. Proven product expertise coupled with collaborative and highly-experienced support enables Embedian to provide exceptional peace of mind to build and maintain successful products.

For more details on Embedian's service offerings such as: enhanced repair services, extended warranty, Embedian training academy, and more http://www.embedian.com/index.php?main\_page=standard\_service.

#### **Customer Comments**

If you have any difficulties using this user guide, discover an error, or just want to provide some feedback, contact Embedian support. Detail any errors you find. We will correct the errors or problems as soon as possible and post the revised user guide on our website.

# **Symbols**

The following symbols may be used in this manual

DANGER indicates a hazardous situation which, if not avoided, will result in death or serious injury.

WARNING indicates a hazardous situation which, if not avoided, could result in death or serious injury.

NOTICE indicates a property damage message.

CAUTION indicates a hazardous situation which, if not avoided, may result in minor or moderate injury.

#### Electric Shock!

This symbol and title warn of hazards due to electrical shocks (> 60 V) when touching products or parts of products. Failure to observe the precautions indicated and/or prescribed by the law may endanger your life/health and/or result in damage to your material.

#### ESD Sensitive Device!

This symbol and title inform that the electronic boards and their components are sensitive to static electricity. Care must therefore be taken during all handling operations and inspections of this product in order to ensure product integrity at all times.

#### **HOT Surface!**

Do NOT touch! Allow to cool before servicing.

This symbol indicates general information about the product and the user guide. This symbol also indicates detail information about the specific product configuration.

### For Your Safety

Your new Embedian product was developed and tested carefully to provide all features necessary to ensure its compliance with electrical safety requirements. It was also designed for a long fault-free life. However, the life expectancy of your product can be drastically reduced by improper treatment during unpacking and installation. Therefore, in the interest of your own safety and of the correct operation of your new Embedian product, you are requested to conform with the following guidelines.

### **High Voltage Safety Instructions**

As a precaution and in case of danger, the power connector must be easily accessible. The power connector is the product's main disconnect device.

Warning

All operations on this product must be carried out by sufficiently skilled personnel only.

Electric Shock!

Before installing a non hot-swappable Embedian product into a system always ensure that your mains power is switched off. This also applies to the installation of piggybacks. Serious electrical shock hazards can exist during all installation, repair, and maintenance operations on this product. Therefore, always unplug the power cable and any other cables which provide external voltages before performing any work on this product.

# Special Handling and Unpacking Instruction

NOTICE

ESD Sensitive Device!

Electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

Do not handle this product out of its protective enclosure while it is not used for operational purposes unless it is otherwise protected.

Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where a safe work station is not guaranteed, it is important for the user to be electrically discharged before touching the product with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

It is particularly important to observe standard anti-static precautions when changing piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC or memory backup, ensure that the product is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or conductive circuits on the product.

### **Lithium Battery Precautions**

If your product is equipped with a lithium battery, take the following precautions when replacing the battery.

Danger of explosion if the battery is replaced incorrectly.

- Replace only with same or equivalent battery type recommended by the manufacturer.

- Dispose of used batteries according to the manufacturer's instructions.

### General Instructions on Usage

In order to maintain Embedian's product warranty, this product must not be altered or modified in any way. Changes or modifications to the product, that are not explicitly approved by Embedian and described in this user guide or received from Embedian Support as a special handling instruction, will void your warranty.

This product should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This also applies to the operational temperature range of the specific board version that must not be exceeded. If batteries are present, their temperature restrictions must be taken into account.

In performing all necessary installation and application operations, only follow the instructions supplied by the present user guide.

Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the product then re-pack it in the same manner as it was delivered.

Special care is necessary when handling or unpacking the product. See Special Handling and Unpacking Instruction.

# Quality and Environmental Management

Embedian aims to deliver reliable high-end products designed and built for quality, and aims to complying with environmental laws, regulations, and other environmentally oriented requirements.

# Disposal and Recycling

Embedian's products are manufactured to satisfy environmental protection requirements where possible. Many of the components used are capable of being recycled. Final disposal of this product after its service life must be accomplished in accordance with applicable country, state, or local laws or regulations.

# **WEEE Compliance**

The Waste Electrical and Electronic Equipment (WEEE) Directive aims to:

- Reduce waste arising from electrical and electronic equipment (EEE)

- Make producers of EEE responsible for the environmental impact of their products, especially when the product become waste

- Encourage separate collection and subsequent treatment, reuse, recovery, recycling and sound environmental disposal of EEE

- > Improve the environmental performance of all those involved during the lifecycle of EEE

Environmental protection is a high priority with Embedian.

Embedian follows the WEEE directive

You are encouraged to return our products for proper disposal.

# **Packing List**

Your product package should include the items listed below.

If any of the items below is missing, contact the seller from whom you have purchased the product.

| Packing List           |

|------------------------|

| 1 x pITX-MX8M-Plus SBC |

NOTICE \_

All most update user's manual and software source codes can be downloaded from Embedian's website. No printed or digital CD will be included.

# Ordering Information

| Part Number         | Description                                                             |

|---------------------|-------------------------------------------------------------------------|

| pITX-MX8M-Plus-2G   | Pico-ITX SBC with NXP i.MX8M Plus Quad Core, 2 GByte LPDDR4, 0~60° C    |

| pITX-MX8M-Plus-2G-I | Pico-ITX SBC with NXP i.MX8M Plus Quad Core, 2 GByte LPDDR4, -40°C~85°C |

| pITX-MX8M-Plus-4G   | Pico-ITX SBC with NXP i.MX8M Plus Quad Core, 4 GByte LPDDR4, 0~60° C    |

| pITX-MX8M-Plus-4G-I | Pico-ITX SBC with NXP i.MX8M Plus Quad Core, 4 GByte LPDDR4, -40°C~85°C |

# **Optional Accessories**

| Part Number       | Description                                                                                                                          |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 125021500AUD-00   | Audio HP Out, Mic In and Line In Cable                                                                                               |

| VTT-HS-9A981-A1   | Heat Sink for pITX-MX8M-PLUS                                                                                                         |

| 125040700LCD-00   | 7-inch LVDS Display G070VW01 V0                                                                                                      |

| 125023000LVD-00   | LVDS Cable for 7-inch G070VW01 V0                                                                                                    |

| 125022000BKT-00   | LVDS Backlight Cable for 7-inch G070VW01 V0                                                                                          |

| 12605M200ABG-00   | M.2 WiFi Module (IEEE 802.11a/b/g/n/ac Wireless LAN 2T2R and Bluetooth 5.3 Combo Module with 88W8997 chipset)                        |

| pITX-IOB-2201     | 50-pin IO Extension Board with 2 x CAN, 4 x RS232, 1 x RS484 (Terminal Blocks), 1 x USB 2.0 Type-A, 1 x USB 2.0+3.0 Type-A, SPI, I2C |

| 126010101245-00   | Dipole Ant. D.B 2.4/5G WIFI 3dBi SMA/M BLK                                                                                           |

| 12506100003HF4-00 | Antenna Cable SMA (F) to MHF4 (F), 100mm                                                                                             |

# Table of Contents

| USER | GUIDE                                     | 1  |

|------|-------------------------------------------|----|

|      | pITX-MX8M-PLUS USER GUIDE                 | 3  |

| Ir   | ntended Use                               | 4  |

| R    | Pevision History                          | 5  |

| T    | erms and Conditions                       | 5  |

| C    | ustomer Support                           | 5  |

| C    | ustomer Service                           | 5  |

| C    | ustomer Comments                          | 5  |

| S    | iymbols                                   | 6  |

|      | or Your Safety                            |    |

|      |                                           |    |

| Н    | ligh Voltage Safety Instructions          | /  |

| S    | pecial Handling and Unpacking Instruction | 7  |

| Li   | ithium Battery Precautions                | 8  |

| G    | ieneral Instructions on Usage             | 8  |

| Q    | uality and Environmental Management       | 8  |

| D    | Disposal and Recycling                    | 8  |

| V    | VEEE Compliance                           | 9  |

| P    | Packing List                              | 10 |

| 0    | Ordering Information                      | 10 |

| 0    | Optional Accessories                      | 11 |

| C    | hapter 1 General Information              | 15 |

| 1.   |                                           |    |

| 1.   |                                           |    |

| 1.   | •                                         |    |

|      | .4 Product Variants                       |    |

| 1.   | .5 Block Diagram                          | 22 |

| 1.   | .6 Mechanical Drawing                     | 23 |

| 1.   | .7 Software Installation and Support      | 26 |

| C    | hapter 2 Hardware Configuration           | 28 |

| 2.1 Jumpers                          | 28 |

|--------------------------------------|----|

| 2.1 Jumpers                          | 31 |

| 2.3 LED                              | 34 |

| 2.4 EEPROM                           | 36 |

| 2.5 Passive Cooler (VTT-HS-9A981-A1) | 37 |

| Chapter 3 Coastline I/O Connectors   | 39 |

| 3.1 Connector Locations              | 39 |

| 3.2 List of Connectors               | 39 |

| 3.3 Connector Pin Assignments        | 40 |

| Chapter 4 Internal I/O Connectors    | 54 |

| 4.1 Connector Locations              | 54 |

| 4.2 List of Connectors               |    |

| 4.3 Connector Pin Assignments        | 56 |

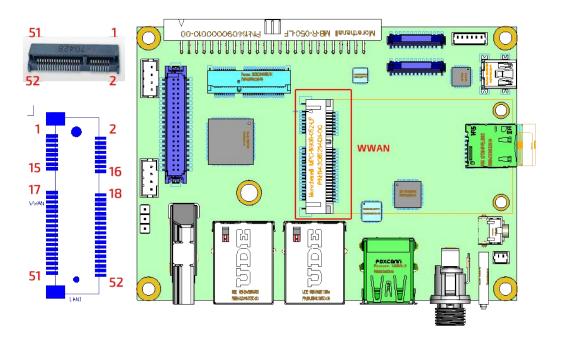

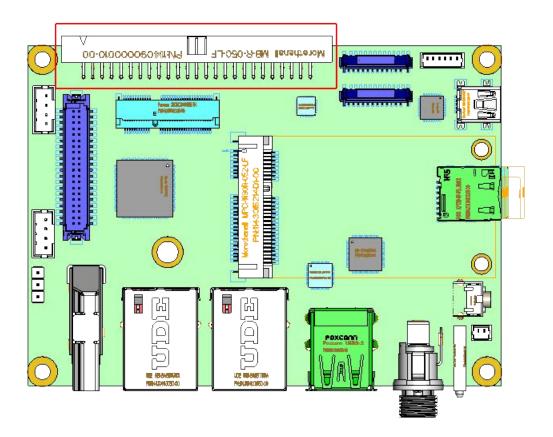

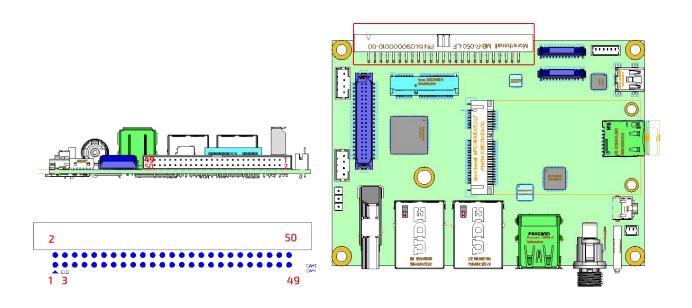

| Chapter 5 Rear EI050 Connector       |    |

| 5.1 Connector Locations              | 85 |

| 5.2 Connector Pin Assignments        | 86 |

# **General Information**

The information provided in this chapter includes:

- Introduction

- Features and Functionality

- Product View

- Product Variants

- Block Diagram

- Mechanical Drawing

- Software Installation and Support

# Chapter 1 General Information

#### 1.1 Introduction

This manual describes the pico-ITX board from NXP i.MX8M Plus processor, which is the first Cortex\*-A53 based SoC integrated with NPU (Neural Processing Unit). This board will also be denoted pITX-MX8M-Plus within this Users Guide.

pITX-MX8M-Plus is capable of providing outstanding Edge AI inference at 2.3 TOPS to perform well on Object Detection as well as Image Segmentation. The use of this Users Guide implies a basic knowledge of PC hardware. This manual is focused on describing the pITX-MX8M-Plus board's special features and is not intended to be a standard PC textbook.

New users are recommended to study the short installation procedure stated in the last chapter before switchingon the power. Latest revision of this manual, datasheet, BSPs (Board Support Packages) can be downloaded from Embedian Web Page. All IO mappings to i.MX8M Plus that are especially usefully for software engineers are also described in this manual.

Upon the standard I/Os on the coastline, pITX-MX8M-Plus also offers the possibility of I/O Extension on the rear side by a 50-pin 2.00mm box header (EIO50) to provide flexible I/Os like more USB, I2C, RS232/285, SPI and CAN for your specific vertical requirements. Users can download the reference design of EIO50 expansion board from Embedian's website.

#### 1.2 Features and Functionality

The board is based on the NXP's quad core ARM Cortex-A53 i.MX8M Plus processor. It is mechanically compliant to the Pico-ITX (pITX) specification. Board key features are:

- Form Factor: pico-ITX and passive cooling solution

- Processor: NXP i.MX8M Plus Quad ARM Core Cortex-A53 (Up to 1.8GHz)

- Memory:

- o Capacity and Technology: 2GB or 4GB LPDDR4 4000MT/s (6GB optional)

- o Flash: 16GB eMMC

- o EEPROM: 4M (to store board part number, revision number, serial number and MAC address)

- > NPU: 2.3 TOPS Neural Network performance

- Display:

- o HDMI: 1 x HDMI 2.0a, up to 3840 x 2160 at 30Hz

- o LVDS: 1 x Single Channel or 1 x Dual Channel 24 bit Bit LVDS, Backlight Power 5V or 12V, Max. 1.5A

- o MIPI-DSI: 14-Lane MIPI-DSI (shared with second channel LVDS interface)

- Graphic Engine

- o GC7000UL with 2D/3D Graphic Acceleration supporting 1G Pixel/s

- o OpenVG 1.1, OpenGL ES3.1, Vulkan, and OpenCL 1.2 FP

- ➤ H/W Video Codec:

- Decoder: 1080p60 HEVC/H.265 Main, VP9 Profile 0/2, VP8, AVC/H.264 Baseline/Main/High

- o Encoder: 1080p60 AVC/H.264, HEVC/H.265

- > 2 x Ethernet (RJ-45):

- o Chipset: NXP i.MX8M Plus integrated RGMII

- o One supports QoS with TSN

- Speed: 10/100/1000 Mbps

- o PHY: Realtek RTL8211FD(I)-CG

- Watchdog Timer:

- o Chipset: TI TPS3828-33DBVR

- o 200ms timeout timer

#### (Continued)

- > TPM: TPM2.0 (ST33HTPH2X32AHE1)

- > Audio:

- Audio Codec WM8960

- Headphone Out

- o Microphone In

- > RTC: RTC Backup Battery by 2-pin type connector

- Reset: 1 Reset Button

- ► 10:

- o USB: 2 x USB 3.1 Gen 1 Host (Type A), 1x USB client (Mini Type B)

- o UART: 1 x UART as debug console by pin header

- o Camera Input: 2 x 4-Lane MIPI-CSI2

- Rear IO:

- o EI050 50-pin 2.00mm Box Header

- 1x USB 3.1 Host, 3 x USB 2.0 Host, 2 x CAN-FD, 1x SPI, 2 x I2C, 4 x UARTs and 6 x GPIOs

- LED:

- 1 x Green Power LED

- o 1 x Yellow Programmable LED

- > Expansion:

- o 1 Mini-PCIe: 1 x Full Size Mini-PCIe Slot (USB 3.1 and USB 2.0 Signals only)

- o 1 M.2 2230 Key E Slot (USB 2.0/I2C/UART/PCIe/UART/SDI0/I2S)

- EIO50 50-pin 2.00mm Box Header (4 x UARTs, 1 x USB 3.1, 2 x USB 2.0, 2 x I2C, 1 x SPI, 6 GPIOs, 2 x CAN-FD)

- o SD Socket: 1 x Micro SD Socket

- o SIM Slot: 1 x Nano SIM Slot

- Power:

- o Power Supply Voltage: 12V DC-IN by lockable DC Jack (or 2-pin type connector by BOM option)

- Power Consumption: 7.21 W

#### (Continued)

#### > Environment:

- $\circ$  Operational Temperature: 0° ~ 60° C (Commercial) / -40° ~ 85° C (Industrial)

- Operating Humidity: 5% ~ 95% Relatively Humidity, non-condensing

#### Mechanical:

- $\circ$  Dimensions: 100 x 72 x 19 mm

- o Weight: 0.05Kg (0.25Kg with Heat Sink)

- Operating System: Yocto, Debian and Android

- Certifications: CE/ FCC Class B

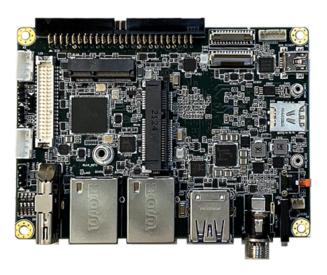

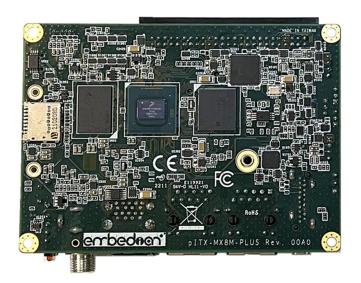

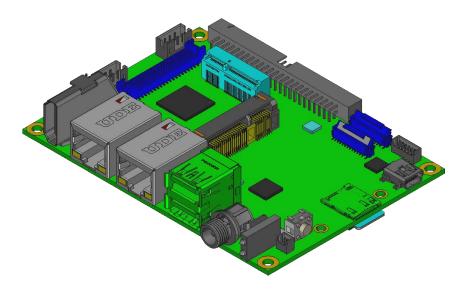

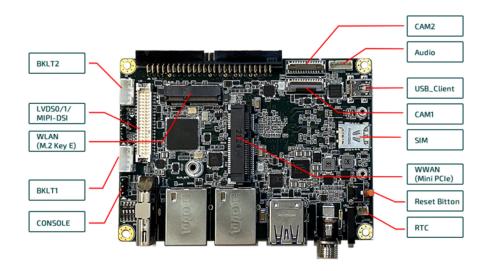

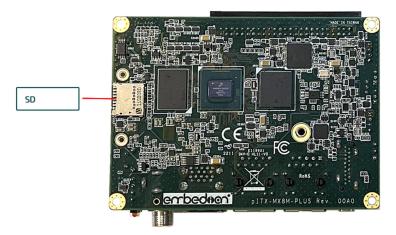

#### 1.3 Product View

Figure 1: pITX-MX8M-Plus Product View (Top View)

Figure 2: pITX-MX8M-Plus Product View (Front View)

Figure 3: pITX-MX8M-Plus Product View (Rear View)

Figure 4: pITX-MX8M-Plus Product View (Bottom View)

#### 1.4 Product Variants

$\label{lem:embedian} \mbox{Embedian offers the pITX-MX8M-Plus in five different configurations}.$

| Part Number         | Description                                                                                                                                         |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| pITX-MX8M-Plus-2G   | Pico-ITX SBC with NXP i.MX8M Plus Quad Core Cortex®-A53 1.8 GHz with NPU, GPU, and VPU, commercial temperature range, 2 GByte LPDDR4, 16 GByte eMMC |

| pITX-MX8M-Plus-2G-I | Pico-ITX SBC with NXP i.MX8M Plus Quad Core Cortex®-A53 1.6 GHz with NPU, GPU, and VPU, industrial temperature range, 2 GByte LPDDR4, 16 GByte eMMC |

| pITX-MX8M-Plus-4G   | Pico-ITX SBC with NXP i.MX8M Plus Quad Core Cortex®-A53 1.8 GHz with NPU, GPU, and VPU, commercial temperature range, 4 GByte LPDDR4, 16 GByte eMMC |

| pITX-MX8M-Plus-4G-I | Pico-ITX SBC with NXP i.MX8M Plus Quad Core Cortex®-A53 1.6 GHz with NPU, GPU, and VPU, industrial temperature range, 4 GByte LPDDR4, 16 GByte eMMC |

Please do not operate the pITX-IMX8M without sufficient cooling system.

Please contact Embedian sales person if you need other memory and flash configurations.

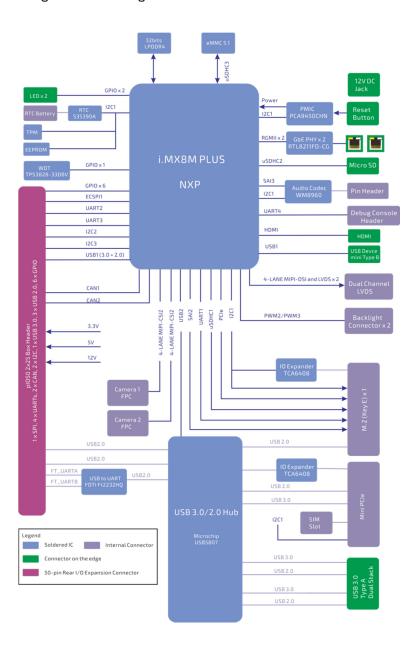

# 1.5 Block Diagram

Overall system block diagram is shown as figure 5.

Figure 5: Block Diagram

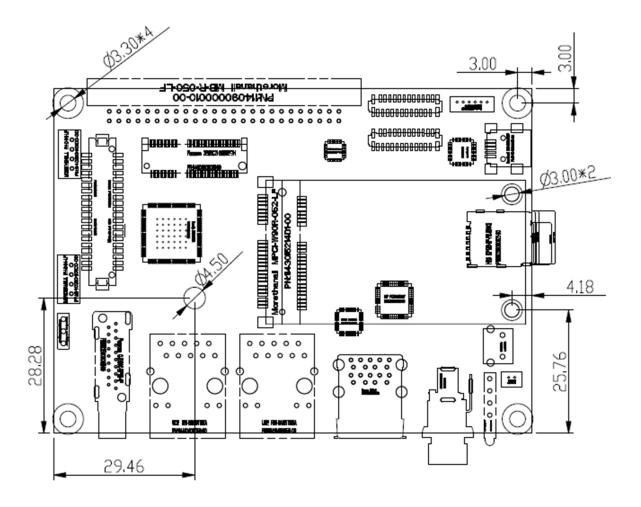

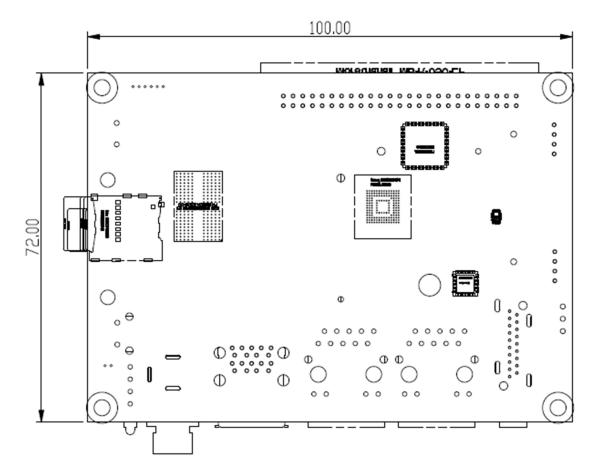

### 1.6 Mechanical Drawing

Overall system mechanical drawings are shown in the following figures.

Figure 6: Mechanical Drawing (Top View)

Figure 7: Mechanical Drawing (Bottom View)

Figure 8: Mechanical Drawing (Side View)

3D .stp or .igs model are available from Embedian's website.

# 1.7 Software Installation and Support

Embedian supports and keeps updating the most recent BSP from NXP. All most update software source codes, build and installation instructions can be found at the development center on Embedian's website. Please also contact the sales person for the technical support windows.

# **Hardware Configuration**

This section contains general information about:

- Jumpers

- Switches

- ▶ LEDs

- ➤ EEPROM

- Passive Cooler

# Chapter 2 Hardware Configuration

This chapter gives the definitions and shows the positions of jumpers, switched, LED and EEPROM. All of the configuration jumpers on the board are in the proper position.

#### 2.1 Jumpers

The pITX-MX8M-Plus has a number of jumpers that allow you to configure your system to suit your application. All use 2mm shorting blocks (shunts) to select settings. Turn off power to the pITX-MX8M-Plus before changing the position of a shunt.

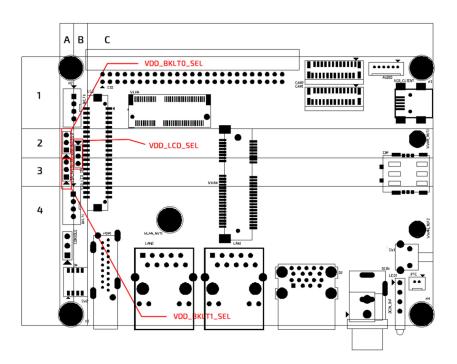

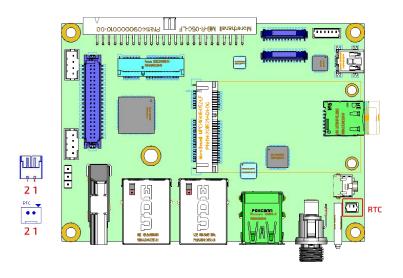

#### 2.1.1 Jumper Location

Figure 9 Jumper Location

#### 2.1.2. List of Jumpers

The table below lists the function of various jumpers.

| Label         | Function                              |

|---------------|---------------------------------------|

| VDD_BKLT0_SEL | 5V/12V LVDS LCD Backlight Voltage     |

| VDD_BKLT1_SEL | 5V/12V MIPI-DSI LCD Backlight Voltage |

| VDD_LCD_SEL   | 3.3V/5V LVDS/MIPI-DSI LCD VDD Voltage |

# 2.1.3. Jumper Settings

The following tables describe how the jumper shunts to various configurations.

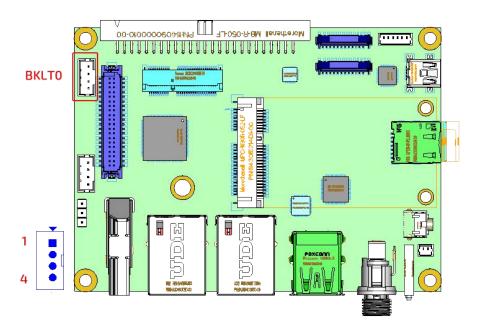

VDD\_BKLT0\_SEL: Location on Board, A2

| VDD_BKLT0_SEL | 5V/12V LVDS LCD Backlight Voltage |               |

|---------------|-----------------------------------|---------------|

|               | Setting                           | Function      |

|               | VDD_BKLTO_SEL (1-2)               | 5V            |

| •             | VDD_BKLTO_SEL (2-3)               | 12V (Default) |

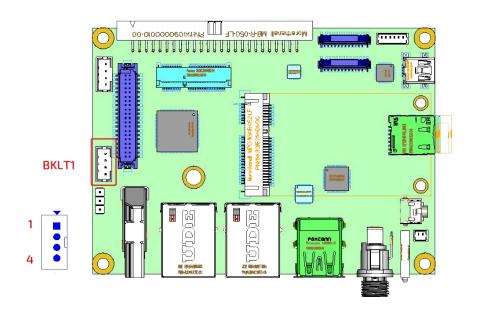

**VDD\_BKLT1\_SEL:** Location on Board, A3

| VDD_BKLT1_SEL | 5V/12V MIPI-DSI LCD Backlight Voltage |          |

|---------------|---------------------------------------|----------|

|               | Setting                               | Function |

|               | VDD_BKLT1_SEL (1-2)                   | 5V       |

| •             | VDD_BKLT1_SEL (2-3)                   | 12V      |

VDD\_LCD\_SEL: Location on Board, B2, B3

| VDD_LCD_SEL | 3.3V/5V LVDS/MIPI-DSI LCD VDD Voltage |                |

|-------------|---------------------------------------|----------------|

|             | Setting                               | Function       |

|             | VDD_LCD_SEL (1-2)                     | 3.3V (Default) |

| •           | VDD_LCD_SEL (2-3)                     | 5V             |

#### 2.1.4. Setting Jumpers

You configure your board to match the needs of your application by setting jumpers. A jumper is the simplest kind of electric switch. It consists of two metal pins and a small metal clip (often protected by a plastic cover) that slides over the pins to connect them. To "close" a jumper you connect the pins with the clip.

To "open" a jumper you remove the clip. Sometimes a jumper will have three pins, labeled 1, 2 and 3. In this case you would connect either pins 1 and 2 or 2 and 3.

The jumper settings are schematically depicted in this manual as follows.

A pair of needle-nose pliers may be helpful when working with jumpers. If you have any doubts about the best hardware configuration for your application, contact your sales representative before you make any change.

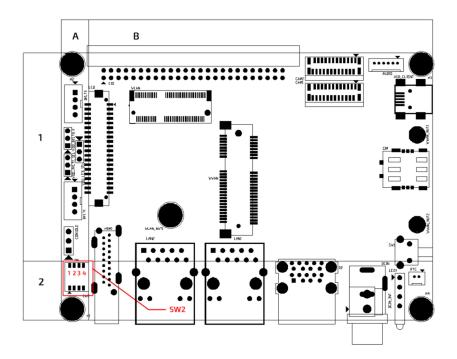

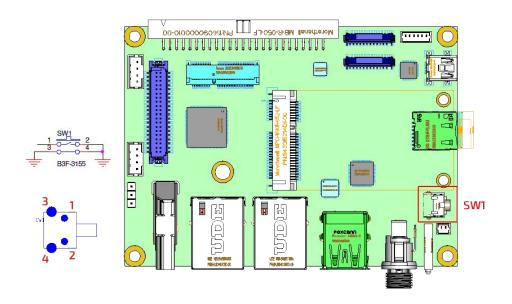

#### 2.2 Switches

The pITX-MX8M-Plus has one 4-port switch allow you to select where to boot up the board and configure the USB1\_ID to determine USB1 as a USB 3.0 host (to EIO50 expansion connector) or client port (mini type B).

#### 2.2.1 Switch Location

Figure 10 Switch Location

#### 2.2.2. List of Switches

The table below lists the function of various jumpers.

| Label   | Function                                                                                                                                                               |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SW2.1-3 | Port 1-3: Boot Select                                                                                                                                                  |  |

| SW2.4   | Port4: Pull USB1_ID to High (Switch OFF) or Low (Switch ON) to configure USB1 as a USB 3.0 host (to the EIO50 50-pin expansion connector) or USB Client (mini type B). |  |

#### 2.2.3. Switch Settings

The following tables describe the switch configurations.

SW2: Location on Board, A2

| SW2           | Setting |    |     | Function                |  |

|---------------|---------|----|-----|-------------------------|--|

| Port 1-3      | 1       | 2  | 3   | Boot Select             |  |

| ON<br>1 2 3 4 | ON      | ON | ON  | Boot from Micro SD card |  |

|               | OFF     | ON | OFF | Boot from eMMC flash    |  |

#### NOTICE

The first stage bootloader in the CPU ROM will read port 1 and port 2 configurations and decide where to load the second stage booloader (u-boot). If (port 1, port 2) is set (ON, ON), it will load from micro SD card. If (port 1, port 2) is set (OFF ON), it will load from eMMC flash.

Once the second stage booloader (u-boot) is loaded, it will read port 3 configuration and decide where to load the Linux kernel. If port 3 is set high, the u-boot will load Linux kernel from micro SD card. Otherwise, it will load Linux kernel from eMMC flash.

#### SW2: Location on Board, A2

| SW2           | Setting | Function                                                                                                   |

|---------------|---------|------------------------------------------------------------------------------------------------------------|

| Port 4        | 4       | USB_ID                                                                                                     |

| ON<br>1 2 3 4 | ON      | USB1_ID is low. USB1 signals from i.MX8M Plus will go to EI050 connector and serve as a USB host.          |

|               | OFF     | USB1_ID is high. USB1 signals from iMX8M Plus will go to mini type B connector and serve as a client port. |

NOTICE

There are two USB 3.0/2.0 (USB1 and USB2) in i.MX8M Plus processor. USB2 connects to Microchip USB 5807C USB3.0/2.0 hub as shown in the block diagram. USB1 goes either to El050 connector or USB client connector.

#### 2.2.4. Setting Switches

You configure your board to match the needs of your application by setting switches.

The diagram in the left shows switches off.

The diagram in the left shows switches on.

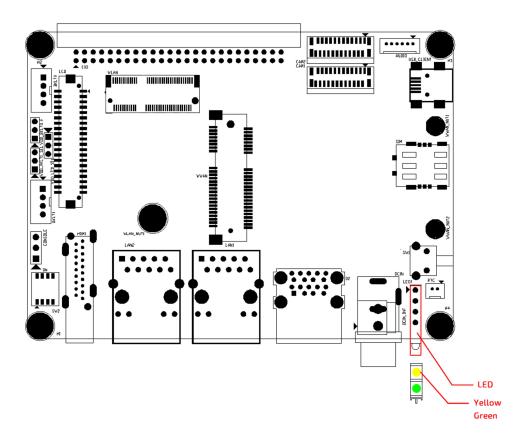

#### 2.3 LED

The pITX-MX8M-Plus implements a 2mm bi-level yellow/green LEDs. One (green) indicates the power status and the other (yellow) is free for use by user defined.

#### 2.3.1 LED Location

Figure 11 LED Location

# 2.3.2. LED Settings

The following tables describe the LED configurations.

| LED    |                           |      |                    | Description       |  |

|--------|---------------------------|------|--------------------|-------------------|--|

| Green  |                           |      |                    | Show power status |  |

|        | NXP i.MX8M Plus Processor |      |                    |                   |  |

| Yellow | Ball                      | Mode | Pin Name           | User Programmable |  |

|        | AD8                       | ALT5 | I2C4_SDAGPI05_I021 |                   |  |

#### 2.4 EEPROM

The pITX-MX8M-Plus SBC includes an I2C serial EEPROM available on the I2C1 bus. An On Semiconductor 24C32 or equivalent EEPROM is used. The device operates at 1.8V. The serial EEPROM is placed at I2C slave addresses address 50 hex.

The serial EEPROM is intended to retain board parameter information, including part number, hardware revision number, serial number, and Ethernet MAC addresses. The module serial EEPROM data structure conforms to the PICMG® EEEP Embedded EEPROM Specification.

#### Note:

The EEPROM ID memory layout is now follow the mainline and as follows.

| Name              | Size (Bytes) | Contents                                                                                                                                                                                                                                                                 |

|-------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Header            | 4            | MSB 0xEE3355AA LSB                                                                                                                                                                                                                                                       |

| Board Name        | 8            | Name for Board in ASCII  "PITX8MP4" = pITX-MX8M-Plus Commercial Temperature with  4GB LPDDR4 Configuration  "PTXI8MP4" = pITX-MX8M-Plus Industrial Temperature with  4GB LPDDR4 Configuration                                                                            |

| Hardware Revision | 4            | Hardware version code for version in ASCII "00A0" = rev. A0                                                                                                                                                                                                              |

| Serial Number     | 12           | Serial number of the board. This is a 12 character string which is: WWYYAABBnnnn  Where: WW = 2 digit week of the year of production  YY = 2 digit year of production  AABB= "PITX" is commercial temp. and "PTXI" is industrial temp.  nnnn = incrementing board number |

| MAC1 Address      | 6            | Ethernet MAC 1 Address                                                                                                                                                                                                                                                   |

| MAC2 Address      | 6            | Ethernet MAC 2 Address                                                                                                                                                                                                                                                   |

NOTICE

The u-boot and Linux kernel will read the Ethernet MAC address in EEPROM.

## 2.5 Passive Cooler (VTT-HS-9A981-A1)

pITX-MX8M-Plus should only operate with a suitable heat sink. Allow to cool down after operation.

Figure 12 Passive Cooler

# Coastline I/O Connectors

This Chapter gives coastline I/O connectors detail information. Section includes:

- Connector Locations

- List of Connectors

- Connector Pin Assignments

# Chapter 3 Coastline I/O Connectors

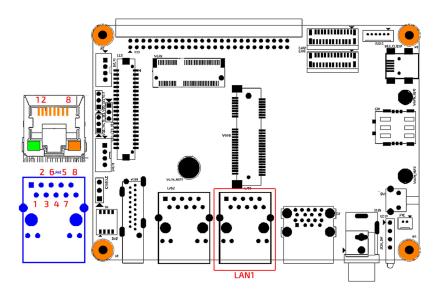

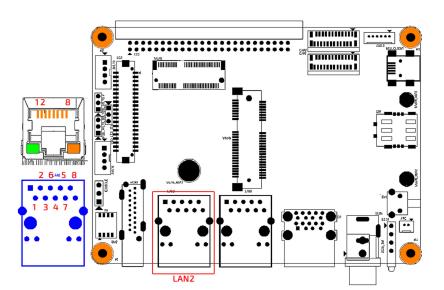

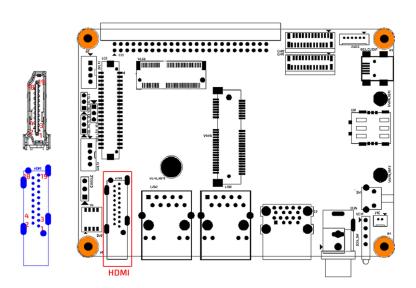

Coast line panel I/O connectors of pITX-MX8M-Plus are described in this section.

#### 3.1 Connector Locations

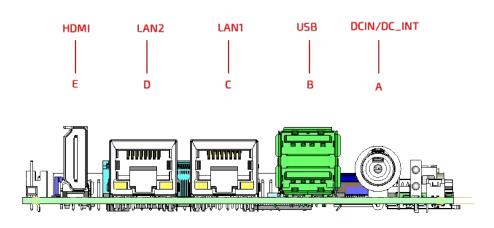

Figure 13 Connector Locations

#### 3.2 List of Connectors

The table below lists the function of various connectors.

| Reference   | Location | Description                                                                         |  |  |

|-------------|----------|-------------------------------------------------------------------------------------|--|--|

| DCIN/DC_INT | А        | 12V DC Power Input by lockable 2.50mm DC Jack (default) /by 3.96mm 2-pin pin Header |  |  |

| USB         | В        | USB 3.0 Type A Connector Dual Stack                                                 |  |  |

| LAN1        | С        | 10/100/1000Mbps Ethernet 1 RJ45 Connector (eth0)                                    |  |  |

| LAN2        | D        | 10/100/1000Mbps Ethernet 2 RJ45 Connector (eth1)                                    |  |  |

| HDMI        | E        | HDMI Connector                                                                      |  |  |

## 3.3 Connector Pin Assignments

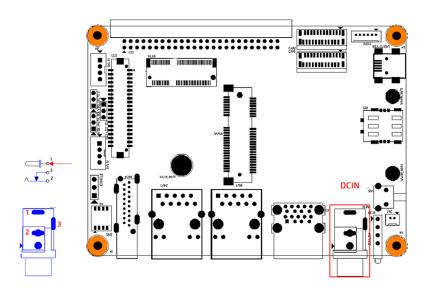

#### 3.3.1 DCIN/DC\_INT (12V DC Power Supply by DC Jack/ 3.96mm 2-pin Header)

Figure 14 DCIN/DC\_INT Connector Locations

The pITX-iMX8M-Plus operates with a 12 V DC +/- 10% power supply. We design DC Jack and 2 Pos 3.96mm Pin Header co-layout, default uses lockable 2.5mm DC Jack.

**DCIN**: Lockable Power Jack Connector

| pin | Assignment | Signal           | Description |

|-----|------------|------------------|-------------|

| 1   | +V12_IN    | +12V Power Input | PWR         |

| 2   | GND        | Power Ground     | PWR         |

| 3   | GND        | Power Ground     | PWR         |

DC\_INT: Internal 2 Pos 3.96mm Power Header Connector

| pin | Assignment | Signal           | Description |

|-----|------------|------------------|-------------|

| 1   | +V12_IN    | +12V Power Input | PWR         |

| 2   | GND        | Power Ground     | PWR         |

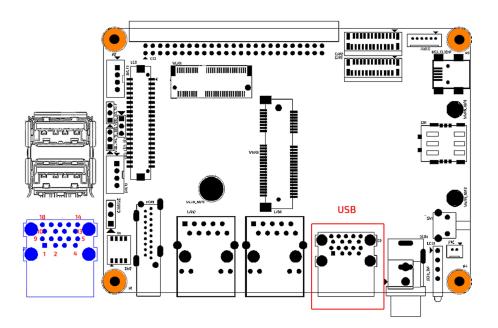

#### 3.3.2 USB

pITX-iMX8MP-Plus board supports a dual-stacked USB3.0 interface. Both ports can reach 5 Gbps speed (Super Speed).

| pin | Assignment     | Signal | Description                                       |  |

|-----|----------------|--------|---------------------------------------------------|--|

| 1   | +VBUS_USB5_TOP | PWR    | USB 5V Power Distribution to downstream device.   |  |

| 2   | USB_TOP_D-     | BIDIR  | USB3 HUB P1 differential USB 2.0 data             |  |

| 3   | USB_TOP_D+     | BIDIR  | USB3 HUB P1 differential USB 2.0 data+.           |  |

| 4   | GND_TOP        | PWR    | Ground                                            |  |

| 5   | USB_TOP_SSRX-  | INPUT  | USB3 HUB P1 differential USB 3.0 receive data     |  |

| 6   | USB_TOP_SSRX+  | INPUT  | USB3 HUB P1 differential USB 3.0 receive data+.   |  |

| 7   | GND_DRAIN_TOP  | PWR    | Ground                                            |  |

| 8   | USB_TOP_SSTX-  | ОИТРИТ | USB3 HUB P1 differential USB 3.0 transmit data    |  |

| 9   | USB_TOP_SSTX+  | OUTPUT | USB3 HUB P1 differential USB 3.0 transmit data +. |  |

| 10  | +VBUS_USB5_BOT | PWR    | USB 5V Power Distribution to downstream device.   |  |

| 11  | USB_BOT_D-     | BIDIR  | USB3 HUB P2 differential USB 2.0 data             |  |

| 12  | USB_BOT_D+     | BIDIR  | USB3 HUB P2 differential USB 2.0 data+.           |  |

| 13  | GND_BOT        | PWR    | Ground                                            |  |

| 14  | USB_BOT_SSRX-  | INPUT  | USB3 HUB P2 differential USB 3.0 receive data     |  |

| 15  | USB_BOT_SSRX+  | INPUT  | USB3 HUB P2 differential USB 3.0 receive data+.   |  |

| 16  | GND_DRAIN_BOT  | PWR    | Ground                                            |  |

| 17  | USB_BOT_SSTX-  | ОИТРИТ | USB3 HUB P2 differential USB 3.0 transmit data    |  |

| 18  | USB_BOT_SSTX+  | OUTPUT | USB3 HUB P2 differential USB 3.0 transmit data +. |  |

#### NOTICE

There are two USB 3.0 compliant instances (USB1 and USB2) in i.MX8M Plus processor.

The USB1 from i.MX8M Plus operates in following modes and goes to either EI050 expansion connector or mini type B connector. It can be configured as one of the following modes.

Host Mode: SS/HS/FS/LS

• Device Mode: SS/HS/FS

• OTG: HS/FS/LS

USB2 from i.MX8M Plus connects to Microchip USB 5807C 7-port USB3.0/2.0 hub and operates as USB 3.0 host only.

The signals in this dual-stacked USB3.0 connector are from port 1 (top) and port 2 (bottom) of the USB5807C hub.

## 3.3.3 LAN1 (Ethernet eth0)

LAN1 supports 10/100/1000 Mbit/s.

Figure 16 Ethernet Connector RJ-45 Jack with Integrated Magnetic

| pin | Assignment                                                  | Description                                                 |  |  |

|-----|-------------------------------------------------------------|-------------------------------------------------------------|--|--|

| 1   | LAN1_MDI0+                                                  | Differential Transmit/Receive Positive Channel 0            |  |  |

| 2   | LAN1_MDI0- Differential Transmit/Receive Negative Channel 0 |                                                             |  |  |

| 3   | LAN1_MDI1+                                                  | Differential Transmit/Receive Positive Channel 1            |  |  |

| 4   | LAN1_MDI2+                                                  | Differential Transmit/Receive Positive Channel 2            |  |  |

| 5   | LAN1_MDI2-                                                  | Differential Transmit/Receive Negative Channel 2            |  |  |

| 6   | LAN1_MDI1-                                                  | Differential Transmit/Receive Negative Channel 1            |  |  |

| 7   | LAN1_MDI3+                                                  | LAN1_MDI3+ Differential Transmit/Receive Positive Channel 3 |  |  |

| 8   | LAN1_MDI3-                                                  | Differential Transmit/Receive Negative Channel 3            |  |  |

#### 3.3.3.1 LAN1 LEDs

The LAN1 LED signals are described as follows.

|        | Description                             |  |  |

|--------|-----------------------------------------|--|--|

| Green  | Off = no receive or transmit activities |  |  |

|        | On = receive or transmit activity       |  |  |

| Orange | Off = no link, 10/100Base-T Link        |  |  |

|        | On = 1000Base-T Link                    |  |  |

#### 3.3.3.2 Path of LAN1

The first 10/100/1000Mbps LAN is implemented from RGMII2 interface of i.MX8M Plus processor that connecting to a Realtek RTL8211FD(I)-CG Ethernet PHY. The implementation from i.MX8M Plus to RTL8211FD(I)-CG is show in the following table.

|      | NXP i.MX8M Plus Processor RGMII2 |                                 | Realtek<br>RTL8211FD(I)-<br>CG |             | Description                                                                                                     |

|------|----------------------------------|---------------------------------|--------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------|

| Ball | Mode                             | Pin Name                        | Pin<br>#                       | Pin<br>Name |                                                                                                                 |

| AJ8  | ALT4                             | SAI1_RXD3 ENET1_MDIO            | 14                             | MDIO        | Serial Management Interface data input/output                                                                   |

| AH9  | ALT4                             | SAI1_RXD2 ENET1_MDC             | 13                             | MDC         | Serial Management Interface clock                                                                               |

| AD10 | ALT4                             | SAI1_RXD4<br>ENET1_RGMII_RD0    | 25                             | RXD0        | Bit 0 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AE10 | ALT4                             | SAI1_RXD5 ENET1_RGMII_RD1       | 24                             | RXD1        | Bit 1 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AH10 | ALT4                             | SAI1_RXD6<br>ENET1_RGMII_RD2    | 23                             | RXD2        | Bit 2 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AH12 | ALT4                             | SAI1_RXD7ENET1_RGMII_RD3        | 22                             | RXD3        | Bit 3 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AJ12 | ALT4                             | SAI1_TXC ENET1_RGMII_RXC        | 27                             | RXC         | Reference clock                                                                                                 |

| AF12 | ALT4                             | SAI1_TXFS<br>ENET1_RGMII_RX_CTL | 26                             | RXCTL       | Indicates both the receive data valid (RXDV) and receive error (RXER) functions per the RGMII specification.    |

| AH14 | ALT4                             | SAI1_TXD4<br>ENET1_RGMII_TX_CTL | 19                             | TXCTL       | Indicates that valid transmission data is present on TXD[3:0].                                                  |

| AJ11 | ALT4                             | SAI1_TXDO<br>ENET1_RGMII_TDO    | 18                             | TXD0        | The MAC transmits data to the transceiver using this signal.                                                    |

| AJ10 | ALT4                             | SAI1_TXD1<br>ENET1_RGMII_TD1    | 17                             | TXD1        | The MAC transmits data to the transceiver using this signal.                                                    |

| AH11 | ALT4                             | SAI1_TXD2<br>ENET1_RGMII_TD2    | 16                             | TXD2        | The MAC transmits data to the transceiver using this signal.                                                    |

| AD12 | ALT4                             | SAI1_TXD3<br>ENET1_RGMII_TD3    | 15                             | TXD3        | The MAC transmits data to the transceiver using this signal.                                                    |

| AH14 | ALT4                             | SAI1_TXD5<br>ENET1_RGMII_TXC    | 20                             | TXC         | Used to latch data from the MAC into the<br>PHY.<br>1000BASE-T: 125MHz<br>100BASE-TX: 25MHz<br>10BASE-T: 2.5MHz |

| AF10 | ALT5                             | SAI1_RXD1<br>GPI04_I003         |                                |             | LAN1 interrupt pin                                                                                              |

The path from RTL8211FD(I)-CG to the RJ45 connector is show in the following table.

| Realtek         |          | RJ45 Connector |            |

|-----------------|----------|----------------|------------|

| RTL8211FD(I)-CG |          |                |            |

| pin             | Pin Name | pin            | Assignment |

| 1               | MDIP0    | 1              | LAN1_MDI0+ |

| 2               | MDINO    | 2              | LAN1_MDI0- |

| 4               | MDIP1    | 3              | LAN1_MDI1+ |

| 5               | MDIN1    | 6              | LAN1_MDI1- |

| 6               | MDIP2    | 4              | LAN1_MDI2+ |

| 7               | MDIN2    | 5              | LAN1_MDI2- |

| 9               | MDIP3    | 7              | LAN1_MDI3+ |

| 10              | MDIN3    | 8              | LAN1_MDI3- |

## 3.3.4 LAN2 (Ethernet eth1)

LAN2 also supports 10/100/1000 Mbit/s. In addition to that, LAN2 also supports QoS with TSN.

Figure 17 Ethernet Connector RJ-45 Jack with Integrated Magnetic

| pin | Assignment | Description                                                 |  |  |  |

|-----|------------|-------------------------------------------------------------|--|--|--|

| 1   | LAN2_MDI0+ | Differential Transmit/Receive Positive Channel 0            |  |  |  |

| 2   | LAN2_MDI0- | LAN2_MDI0- Differential Transmit/Receive Negative Channel 0 |  |  |  |

| 3   | LAN2_MDI1+ | Differential Transmit/Receive Positive Channel 1            |  |  |  |

| 4   | LAN2_MDI2+ | Differential Transmit/Receive Positive Channel 2            |  |  |  |

| 5   | LAN2_MDI2- | Differential Transmit/Receive Negative Channel 2            |  |  |  |

| 6   | LAN2_MDI1- | Differential Transmit/Receive Negative Channel 1            |  |  |  |

| 7   | LAN2_MDI3+ | Differential Transmit/Receive Positive Channel 3            |  |  |  |

| 8   | LAN2_MDI3- | Differential Transmit/Receive Negative Channel 3            |  |  |  |

#### 3.3.4.1 LAN2 LEDs

The LAN2 LED signals are described as follows.

|        | Description                             |  |  |  |

|--------|-----------------------------------------|--|--|--|

| Green  | Off = no receive or transmit activities |  |  |  |

|        | On = receive or transmit activity       |  |  |  |

| Orange | Off = no link, 10/100Base-T Link        |  |  |  |

|        | On = 1000Base-T Link                    |  |  |  |

#### 3.3.4.2 Path of LAN2

The second 10/100/1000 Mbps LAN is implemented from RGMII1 interface of i.MX8M Plus processor that connecting to a Realtek RTL8211FD(I)-CG Ethernet PHY. The implementation from i.MX8M Plus to RTL8211FD(I)-CG is show in the following table.

|      | NXP i.MX8M Plus Processor RGMII2 |                                                          |          | ealtek<br>211FD(I)-<br>CG | Description                                                                                                     |

|------|----------------------------------|----------------------------------------------------------|----------|---------------------------|-----------------------------------------------------------------------------------------------------------------|

| Ball | Mode                             | Pin Name                                                 | Pin<br># | Pin<br>Name               |                                                                                                                 |

| AH29 | ALT0                             | ENET_MDIOENET_QOS_MDIO                                   | 14       | MDIO                      | Serial Management Interface data input/output                                                                   |

| AH28 | ALT0                             | ENET_MDCENET_MDC                                         | 13       | MDC                       | Serial Management Interface clock                                                                               |

| AG29 | ALT0                             | ENET_RDO<br>ENET_QOS_RGMII_RDO                           | 25       | RXD0                      | Bit 0 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AG28 | ALT0                             | ENET_RD1<br>ENET_QOS_RGMII_RD1                           | 24       | RXD1                      | Bit 1 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AF29 | ALT0                             | ENET_RD2<br>ENET_QOS_RGMII_RXD2                          | 23       | RXD2                      | Bit 2 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AF28 | ALT0                             | ENET_RD3<br>ENET_QOS_RGMII_RXD3                          | 22       | RXD3                      | Bit 3 of the 4 data bits that are sent by the transceiver on the receive path.                                  |

| AE29 | ALT0                             | ENET_RXC<br>CCM_ENET_QOS_<br>CLOCK_GENERATE_RX_CLK       | 27       | RXC                       | Reference clock                                                                                                 |

| AE28 | ALT0                             | ENET_RX_CTL<br>ENET_QOS_RGMII_RX_CTL                     | 26       | RXCTL                     | Indicates both the receive data valid (RXDV) and receive error (RXER) functions per the RGMII specification.    |

| B48  | ALT0                             | ENET_TX_CTL<br>ENET_QOS_RGMII_TX_CTL                     | 19       | TXCTL                     | Indicates that valid transmission data is present on TXD[3:0].                                                  |

| AC25 | ALT0                             | ENET_TD0<br>ENET_QOS_RGMII_TD0                           | 18       | TXD0                      | The MAC transmits data to the transceiver using this signal.                                                    |

| AE26 | ALT0                             | ENET_TD1<br>ENET_QOS_RGMII_TD1                           | 17       | TXD1                      | The MAC transmits data to the transceiver using this signal.                                                    |

| AF26 | ALT0                             | ENET_TD2<br>ENET_QOS_RGMII_TD2                           | 16       | TXD2                      | The MAC transmits data to the transceiver using this signal.                                                    |

| AD24 | ALT0                             | ENET_TD3<br>ENET_QOS_RGMII_TD3                           | 15       | TXD3                      | The MAC transmits data to the transceiver using this signal.                                                    |

| AE24 | ALT0                             | ENET_RGMII_TXC<br>CCM_ENET_QOS_<br>CLOCK_GENERATE_TX_CLK | 20       | TXC                       | Used to latch data from the MAC into the<br>PHY.<br>1000BASE-T: 125MHz<br>100BASE-TX: 25MHz<br>10BASE-T: 2.5MHz |

| AH17 | ALT5                             | SAI2_RXFS<br>GPI04_I021                                  |          |                           | LAN2 interrupt pin                                                                                              |

The path from RTL8211FD(I)-CG to the RJ45 connector is show in the following table.

| Realtek         | FD() 66  | RJ45 Connector |            |

|-----------------|----------|----------------|------------|

| RTL8211FD(I)-CG |          |                |            |

| pin             | Pin Name | pin            | Assignment |

| 1               | MDIP0    | 1              | LAN2_MDI0+ |

| 2               | MDINO    | 2              | LAN2_MDI0- |

| 4               | MDIP1    | 3              | LAN2_MDI1+ |

| 5               | MDIN1    | 6              | LAN2_MDI1- |

| 6               | MDIP2    | 4              | LAN2_MDI2+ |

| 7               | MDIN2    | 5              | LAN2_MDI2- |

| 9               | MDIP3    | 7              | LAN2_MDI3+ |

| 10              | MDIN3    | 8              | LAN2_MDI3- |

NOTICE

LAN2 also supports QoS with TSN. NXP offers sample codes and examples to support this feature.

#### 3.3.5 HDMI

pITX-MX8M-Plus supports one HDMI instance. The HDMI is implemented directly from HDMI interface from NXP i.MX8M Plus processor.

Figure 18 HDMI Connector

#### **HDMI**: HDMI Pin Mapping

| pin | Function      | Direction | Description                                                |  |  |

|-----|---------------|-----------|------------------------------------------------------------|--|--|

| 1   | HDMI_D2+      | Out       |                                                            |  |  |

| 2   | GND           | Ground    | TMDS Link Channel 2                                        |  |  |

| 3   | HDMI_D2-      | Out       |                                                            |  |  |

| 4   | HDMI_D1+      | Out       |                                                            |  |  |

| 5   | GND           | Ground    | TMDS Link Channel 1                                        |  |  |

| 6   | HDMI_D1-      | Out       |                                                            |  |  |

| 7   | HDMI_D0+      | Out       |                                                            |  |  |

| 8   | GND           | Ground    | TMDS Link Channel 0                                        |  |  |

| 9   | HDMI_D0-      | Out       |                                                            |  |  |

| 10  | HDMI_CLK+     | Out       |                                                            |  |  |

| 11  | GND           | Ground    | TMDS Clock Channel                                         |  |  |

| 12  | HDMI_CLK-     | Out       |                                                            |  |  |

| 13  | HDMI_CEC      | In/Out    |                                                            |  |  |

| 14  | HDMI_AUX-     | In        | Optional usage as Audio Return Channel                     |  |  |

| 15  | HDMI_DDC_SCL  | Out       | HDMI DDC Serial Clock                                      |  |  |

| 16  | HDMI_DDC_SDA  | In/Out    | HDMI DDC Serial Date                                       |  |  |

| 17  | GND           | Ground    |                                                            |  |  |

| 18  | +5V           | Power     |                                                            |  |  |

| 19  | HDMI_AUX+/HPD | ln        | Hot plug detect, optional usage as Audio Return<br>Channel |  |  |

## Internal I/O Connectors

This Chapter gives internal I/O connectors detail information. Section includes:

- Connector Locations

- List of Connectors

- Connector Pin Assignments

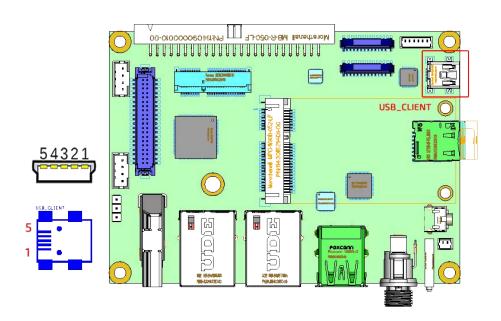

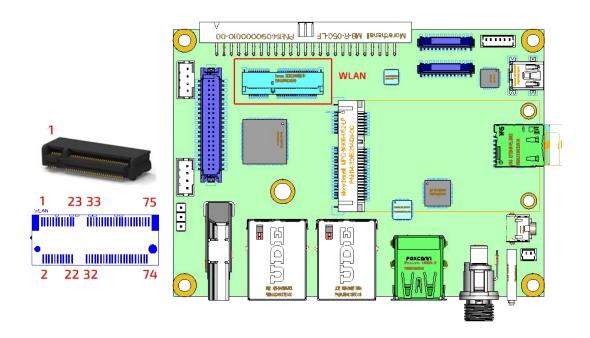

## Chapter 4 Internal I/O Connectors

Internal I/O connectors of pITX-MX8M-Plus are described in this section.

## 4.1 Connector Locations

Figure 19 Connector Locations (Top View)

Figure 20 Connector Locations (Bottom View)

## 4.2 List of Connectors

The table below lists the function of various connectors.

| Reference  | Description                           |

|------------|---------------------------------------|

| RTC        | RTC Battery Connector                 |

| SW1        | Reset Button                          |

| BKLT0      | LVDS Backlight Control Signals        |

| BKLT1      | MIPI-DSI Backlight Control Signals    |

| LCD        | LVDS, MIPI-DSI Connector              |

| CAM1       | MIPI-CSI Camera Input 1 FPC Connector |

| CAM2       | MIPI-CSI Camera Input 2 FPC Connector |

| AUDIO      | Min In and Line Out Connector         |

| USB_CLIENT | USB Client mini Type B Connector      |

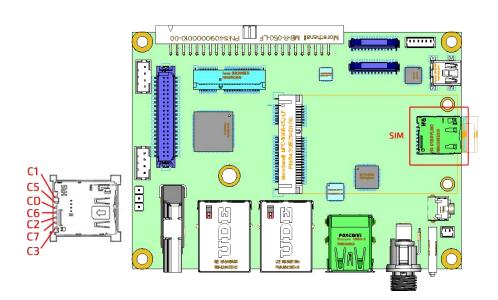

| WLAN       | M2 Key E Connector                    |

| WWAN       | Mini PCIe Connector                   |

| SIM        | Nano SIM Card Slot                    |

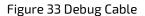

| CONSOLE    | Debug Uart Console Connector          |

| SD         | Micro SD Card Slot                    |

## 4.3 Connector Pin Assignments

## 4.3.1 RTC (RTC Battery 2-pin 1.25mm Connector)

The 2-pin connector has a 1.25 mm pitch.

Figure 21 RTC Battery 2-pin Connector Locations

**RTC**: 2-pin 1.25mm connector (Connector: Molex 0530470210 or compatible. Mating Connector: Molex 0510210200 or compatible)

| pin | Signal    |

|-----|-----------|

| 1   | +COIN_RTC |

| 2   | GND       |

## 4.3.2 SW1 (Reset Button)

Figure 22 RESET Button Locations

SW1: RESET Button

| pin | Signal    |

|-----|-----------|

| 1   | RESET_IN# |

| 2   | GND       |

| 3   | GND       |

| 4   | GND       |

## 4.3.3 BKLT0 (LVDS Backlight Control Signals)

Figure 23 BKLT0 Locations

**BKLTO**: LVDS Backlight Control Signals (Mating Connector: JST PHR-4 or compatible)

| pin | Signal        |           | NXP i.MX8 | Description         |                                 |

|-----|---------------|-----------|-----------|---------------------|---------------------------------|

|     |               | Ball Mode |           | Pin Name            |                                 |

| 1   | VDD_BKLT0     |           |           |                     | Backlight Power                 |

| 2   | LCD0_BKLT_EN  | AC12      | ALT5      | SAI1_TXD6GPI04_I018 | High enables panel<br>backlight |

| 3   | LCD0_BKLT_PWM | AE16 ALT2 |           | SAI5_RXD0PWM2_OUT   | Display backlight PWM control   |

| 4   | GND           |           |           |                     | Ground                          |

## 4.3.4 BKLT1 (MIPI-DSI Backlight Control Signals)

Figure 24 BKLT1 Locations

**BKLT1**: MIPI-DSI Backlight Control Signals (Mating Connector: JST PHR-4 or compatible)

| pin | Signal        |           | NXP i.MX8 | Description         |                                 |

|-----|---------------|-----------|-----------|---------------------|---------------------------------|

|     |               | Ball Mode |           | Pin Name            |                                 |

| 1   | VDD_BKLT1     |           |           |                     | Backlight Power                 |

| 2   | LCD1_BKLT_EN  | AE12      | ALT5      | SAI1_MCLKGPI04_I020 | High enables panel<br>backlight |

| 3   | LCD1_BKLT_PWM | AE18      | ALT1      | SPDIF_TXPWM3_OUT    | Display backlight PWM control   |

| 4   | GND           |           |           |                     | Ground                          |

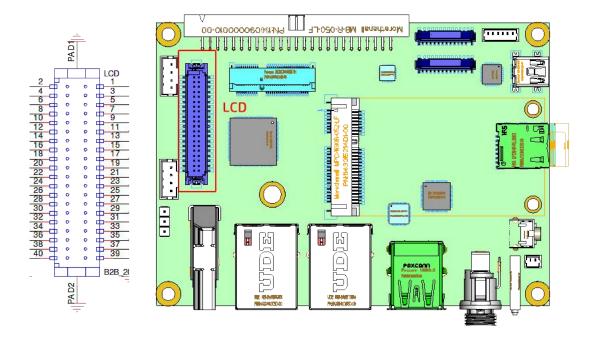

## 4.3.5 LCD (LVDS, MIPI-DSI Connector)

pITX-MX8M-Plus supports one single channel or one Dual Channel 24 bit LVDS LCD display. It also supports one 4-Lane MIPI-DSI interface that shared with LVDS1. All LVDS and MIPI-DSI signals are from i.MX8M Plus processor.

Figure 25 LCD Locations

**LCD**: LVDSO, LVDS1 and MIPI-DSI Signals (Mating Connector: Hirose DF13-40DS-1.25DSA(55) or compatible)

| pin | Signal                     |             | NXP i.MX8M Plus Processor |          | Description                                                  |

|-----|----------------------------|-------------|---------------------------|----------|--------------------------------------------------------------|

|     |                            | Ball        | Mode                      | Pin Name |                                                              |

| 1   | VDD_LCD                    |             |                           |          | LVDS panel VDD                                               |

| 2   | VDD_LCD                    |             |                           |          | LVDS panel VDD                                               |

| 3   | VDD_LCD                    |             |                           |          | LVDS panel VDD                                               |

| 4   | VDD_LCD                    |             |                           |          | LVDS panel VDD                                               |

| 5   | GND                        |             |                           |          | Ground                                                       |

| 6   | GND                        |             |                           |          | Ground                                                       |

| 7   | LVDS0_D0-                  | E28         |                           |          | LVDS0 LCD data channel<br>differential pairs 1-              |

| 8   | LVDS1_D0-/<br>MIPI_DSI_D0- | B26/<br>B16 |                           |          | LVDS1/MIPI-DSI LCD data<br>channel differential pairs 1-     |

| 9   | LVDS0_D0+                  | D29         |                           |          | LVDS0 LCD data channel<br>differential pairs 1+              |

| 10  | LVDS1_D0+/<br>MIPI_DSI_D0+ | A26/<br>A16 |                           |          | LVDS1/MIPI-DSI LCD data<br>channel differential pairs 1+     |

| 11  | GND                        |             |                           |          | Ground                                                       |

| 12  | GND                        |             |                           |          | Ground                                                       |

| 13  | LVDS0_D1-                  | F28         |                           |          | LVDS0 LCD data channel<br>differential pairs 2-              |

| 14  | LVDS1_D1-/<br>MIPI_DSI_D1- | B27/<br>B17 |                           |          | LVDS1/MIPI-DSI LCD data<br>channel differential pairs 2-     |

| 15  | LVDS0_D1+                  | E29         |                           |          | LVDS0 LCD data channel<br>differential pairs 2+              |

| 16  | LVDS1_D1+/<br>MIPI_DSI_D1+ | A27/<br>A17 |                           |          | LVDS1/MIPI-DSI LCD data<br>channel differential pairs 2+     |

| 17  | GND                        |             |                           |          | Ground                                                       |

| 18  | GND                        |             |                           |          | Ground                                                       |

| 19  | LVDS0_D2-                  | H28         |                           |          | LVDS0 LCD data channel<br>differential pairs 3-              |

| 20  | LVDS1_D2-/<br>MIPI_DSI_D2- | C28/<br>B18 |                           |          | LVDS1/<br>MIPI-DSI LCD data channel<br>differential pairs 3- |

## (Continued)

| pin | Signal                     | NXP i.MX8M Plus Processor |      | l Plus Processor | Description                                              |

|-----|----------------------------|---------------------------|------|------------------|----------------------------------------------------------|

|     |                            | Ball                      | Mode | Pin Name         |                                                          |

| 21  | LVDS0_D2+                  | G29                       |      |                  | LVDS0 LCD data channel<br>differential pairs 3+          |

| 22  | LVDS1_D2+/<br>MIPI_DSI_D2+ | B29/<br>A19               |      |                  | LVDS1/MIPI_DSI LCD data<br>channel differential pairs 3+ |

| 23  | GND                        |                           |      |                  | Ground                                                   |

| 24  | GND                        |                           |      |                  | Ground                                                   |

| 25  | LVDS0_CK-                  | G28                       |      |                  | LVDS0 LCD differential clock<br>pairs-                   |

| 26  | LVDS1_CK-                  | B28/<br>B18               |      |                  | LVDS1/MIPI-DSI LCD<br>differential clock pairs-          |

| 27  | LVDS0_CK+                  | F29                       |      |                  | LVDS0 LCD differential clock<br>pairs+                   |

| 28  | LVDS1_CK+                  | A28/<br>A18               |      |                  | LVDS1/MIPI-DSI LCD<br>differential clock pairs+          |

| 29  | GND                        |                           |      |                  | Ground                                                   |

| 30  | GND                        |                           |      |                  | Ground                                                   |

| 31  | LVDS0_D3-                  | J28                       |      |                  | LVDS0 LCD data channel<br>differential pairs 4-          |

| 32  | LVDS1_D3-                  | D29/<br>B20               |      |                  | LVDS1/MIPI_DSI LCD data<br>channel differential pairs 4- |

| 33  | LVDS0_D3+                  | H29                       |      |                  | LVDS0 LCD data channel<br>differential pairs 4+          |

| 34  | LVDS1_D3+                  | C29/<br>A20               |      |                  | LVDS1/MIPI_DSI LCD data<br>channel differential pairs 4+ |

| 35  | GND                        |                           |      |                  | Ground                                                   |

| 36  | GND                        |                           |      |                  | Ground                                                   |

| 37  | I2C2_SCL                   | AH6                       | ALT0 | I2C2_SCLI2C2_SCL | I2C_LCD bus clock                                        |

| 38  | I2C2_SDA                   | AE8                       | ALT0 | I2C2_SDAI2C2_SDA | I2C_LCD bus data                                         |

| 39  | EDPO_HPD                   |                           |      |                  | eDP0 Hot Plug Detect                                     |

| 40  | EDP1_HPD                   |                           |      |                  | eDP1 Hot Plug Detect                                     |

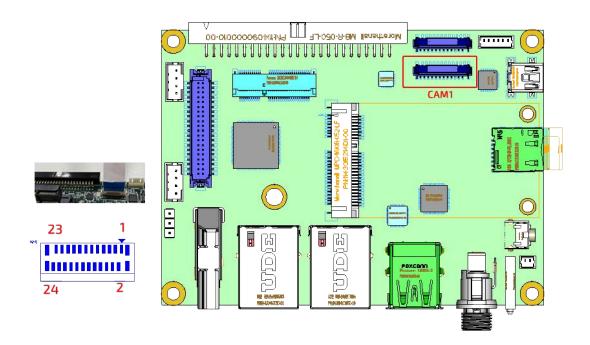

## 4.3.6 CAM1 (MIPI-CSI Camera Input 1 FPC Connector)

pITX-MX8M-Plus supports two MIPI-CSI2 interfaces. The 24-pin 0.5mm FPC connector default supports Google /Coral 5Mpix CAMERA MODULE, Omnivision OV5645. Users can purchase them from Coral's website at https://coral.ai/products/camera/

Figure 26 CAM1 Locations

**CAM1**: MIPI-CSI Camera Input 1 FPC Connector (Connector: Hirose FH12S-50S-0.5SH(55) or compatible)

| pin | Signal          |      | NXP i.MX8M Plus Processor |                       | Description                       |

|-----|-----------------|------|---------------------------|-----------------------|-----------------------------------|

|     |                 | Ball | Mode                      | Pin Name              |                                   |

| 1   | VDD_CAM1        |      |                           |                       | 3.3V CAM1 VDD                     |

| 2   | CAM1_RST#       | L23  | ALT5                      | NAND_DATA01GPI03_I007 | Camera Reset (Active Low)         |

| 3   | CAM1_VSYNC      | AJ18 | ALT5                      | SAI3_RXCGPI04_I029    | CAM1 Vsync.                       |

| 4   | CAM1_I2C_SDA    | AD14 | ALT3                      | SAI5_RXCI2C6_SDA      | I2C Data                          |

| 5   | CAM1_I2C_SCL    | AC14 | ALT3                      | SAI5_RXFSI2C6_SCL     | I2C Clock                         |

| 6   | GND             |      |                           |                       | Ground                            |

| 7   | CAM1_MCK        | A4   | ALT6                      | GPI01_I014CCM_CLK01   | CAM1 MCLK                         |

| 8   | CAM1_PWR#       | R25  | ALT5                      | NAND_DATA00GPI03_I006 | Camera Power Down<br>(Active Low) |

| 9   | GND             |      |                           |                       | Ground                            |

| 10  | MIPI_CSI1_D3_P  | D26  |                           |                       | Differential Data3 P              |

| 11  | MIPI_CSI1_D3_N  | E26  |                           |                       | Differential Data3 N              |

| 12  | GND             |      |                           |                       | Ground                            |

| 13  | MIPI_CSI1_D2_P  | D24  |                           |                       | Differential Data2 P              |

| 14  | MIPI_CSI1_D2_N  | E24  |                           |                       | Differential Data2 N              |

| 15  | GND             |      |                           |                       | Ground                            |

| 16  | MIPI_CSI1_D1_P  | D20  |                           |                       | Differential Data1 P              |

| 17  | MIPI_CSI1_D1_N  | E20  |                           |                       | Differential Data1 N              |

| 18  | GND             |      |                           |                       | Ground                            |

| 19  | MIPI_CSI1_CLK_P | D22  |                           |                       | Differential Clock P              |

| 20  | MIPI_CSI1_CLK_N | E22  |                           |                       | Differential Clock N              |

| 21  | GND             |      |                           |                       | Ground                            |

| 22  | MIPI_CSI1_D0_P  | D18  |                           |                       | Differential Data0 P              |

| 23  | MIPI_CSI1_D0_N  | E18  |                           |                       | Differential Data0 N              |

| 24  | GND             |      |                           |                       | Ground                            |

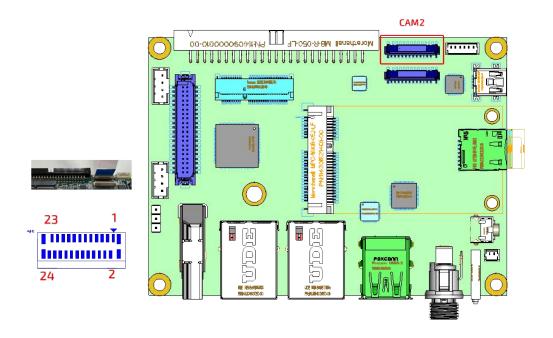

## 4.3.7 CAM2 (MIPI-CSI Camera Input 2 FPC Connector)

The second MIPI-CSI2 interface also uses 24-pin 0.5mm FPC connector and default supports Google /Coral 5Mpix CAMERA MODULE, Omnivision 0V5645.

Figure 27 CAM2 Locations

**CAM2**: MIPI-CSI Camera Input 2 FPC Connector (Connector: Hirose FH12S-50S-0.5SH(55) or compatible)

| pin | Signal          |      | NXP i.MX8M Plus Processor |                       | Description                       |

|-----|-----------------|------|---------------------------|-----------------------|-----------------------------------|

|     |                 | Ball | Mode                      | Pin Name              |                                   |

| 1   | VDD_CAM1        |      |                           |                       | 3.3V CAM2 VDD                     |

| 2   | CAM2_RST#       | N24  | ALT5                      | NAND_DATA03GPI03_I009 | Camera Reset (Active<br>Low)      |

| 3   | CAM2_VSYNC      | AJ9  | ALT5                      | SAI1_RXFSGPI04_I000   | CAM2 Vsync.                       |

| 4   | CAM2_I2C_SDA    | AJ22 | ALT2                      | ECSPI2_SS0I2C4_SDA    | I2C Data                          |

| 5   | CAM2_I2C_SCL    | AH20 | ALT2                      | ECSPI2_MISOI2C4_SCL   | I2C Clock                         |

| 6   | GND             |      |                           |                       | Ground                            |

| 7   | CAM2_MCK        | A4   | ALT6                      | GPI01_I014CCM_CLK01   | CAM2 MCLK                         |

| 8   | CAM2_PWR#       | L24  | ALT5                      | NAND_DATA02GPI03_I008 | Camera Power Down<br>(Active Low) |

| 9   | GND             |      |                           |                       | Ground                            |

| 10  | MIPI_CSI2_D3_P  | B21  |                           |                       | Differential Data3 P              |

| 11  | MIPI_CSI2_D3_N  | A21  |                           |                       | Differential Data3 N              |

| 12  | GND             |      |                           |                       | Ground                            |

| 13  | MIPI_CSI2_D2_P  | B22  |                           |                       | Differential Data2 P              |

| 14  | MIPI_CSI2_D2_N  | A22  |                           |                       | Differential Data2 N              |

| 15  | GND             |      |                           |                       | Ground                            |

| 16  | MIPI_CSI2_D1_P  | B24  |                           |                       | Differential Data1 P              |

| 17  | MIPI_CSI2_D1_N  | A24  |                           |                       | Differential Data1 N              |

| 18  | GND             |      |                           |                       | Ground                            |

| 19  | MIPI_CSI2_CLK_P | A23  |                           |                       | Differential Clock P              |

| 20  | MIPI_CSI2_CLK_N | B23  |                           |                       | Differential Clock N              |

| 21  | GND             |      |                           |                       | Ground                            |

| 22  | MIPI_CSI2_D0_P  | B25  |                           |                       | Differential Data0 P              |

| 23  | MIPI_CSI2_D0_N  | A25  |                           |                       | Differential Data0 N              |

| 24  | GND             |      |                           |                       | Ground                            |

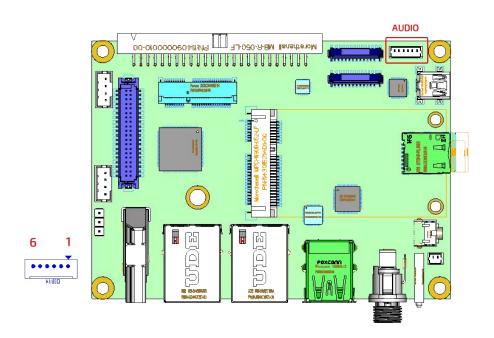

#### 4.3.8 Audio

The audio interface is implemented from SAI3 of i.MX8M Plus and connecting to Cirrus WM8960 Audio Codec.

Figure 28 Audio Connector Locations

**Audio**: 6-pin 1.25mm Audio Connector (Connector: Molex 0530470610 or compatible. Mating Connector: Molex 0510210600 or compatible)

| pin | Assignment | Description             |

|-----|------------|-------------------------|

| 1   | HP_R       | Headphone Right Channel |

| 2   | GND        | Ground                  |