# User's Manual

## SMARC Computer on Module

Freescale i.MX6 Cortex A9

24bits Parallel LCD/LVDS/HDMI

4 x COM Ports

2 x SDHC

1 x USB Host 2.0, 1 x USB OTG

1 x 10/100/1000M Gigabit Ethernet

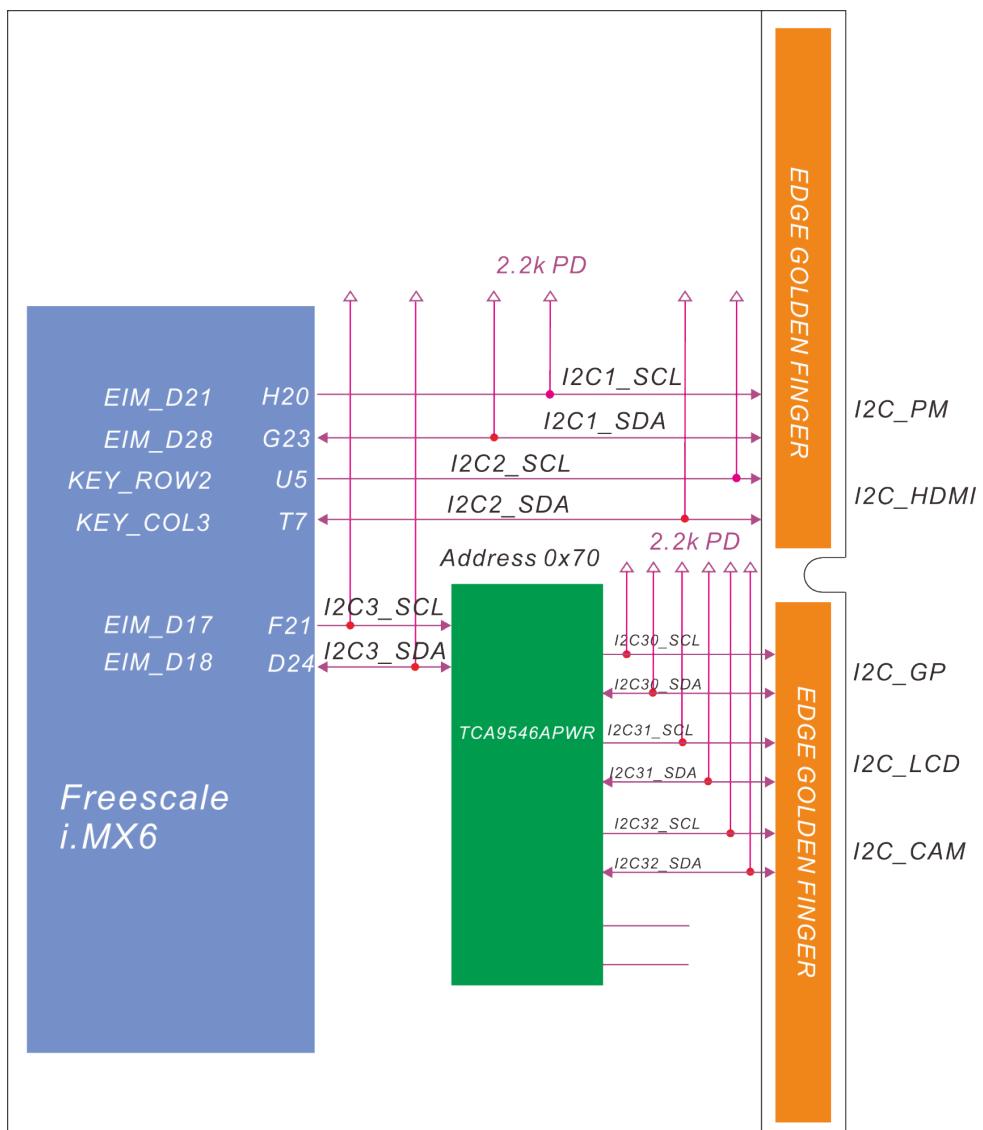

2 x CAN Bus, 2 x SPIs, 4 x I2Cs

1 x PCIe, 1 x SATA, 1 x MIPI

## **SMARC-FiMX6**

**embe<sup>d</sup>ian**

## **Revision History**

| <b>Revision</b> | <b>Date</b> | <b>Changes from Previous Revision</b>                                                                                                      |

|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0             | 2014/11/20  | <i>Initial Release</i>                                                                                                                     |

| 1.2             | 2015/2/25   | <i>Documentation Wording Fixed and add section 2.1.8 and add Ethernet MAC EEPROM information</i>                                           |

| 1.3             | 2015/07/11  | <i>Remove PCIe refclk serial capacitor from hardware revision 00B0 (Figure 8). The serial capacitor should be present on carrier board</i> |

| 1.4             | 2022/04/08  | <i>Change hardware revision to rev. 00C1, change MIPI_CSI from CSI1 to CSI0</i>                                                            |

| 2.0             | 2022/12/20  | <i>Change hardware revision to rev. 00D0: Replace Ethernet PHY from Realtek RTL8211FD-CG to Realtek RTL8211FD-CG</i>                       |

| 2.1             | 2025/12/17  | <i>As 1.8V and 3.3V VDDIO refer to the same item, the part number has been standardized for consistency.</i>                               |

## USER INFORMATION

### *About This Manual*

This document provides information about products from EMBEDIAN, INC. No warranty of suitability, purpose, or fitness is implied. While every attempt has been made to ensure that the information in this document is accurate, the information contained within is supplied "as-is" and is subject to change without notice.

For the circuits, descriptions and tables indicated, EMBEDIAN assumes no responsibility as far as patents or other rights of third parties are concerned.

### *Copyright Notice*

Copyright © 2014 EMBEDIAN, INC..

All rights reserved. No part of this manual may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), without the express written permission of EMBEDIAN.

### *Trademarks*

The following lists the trademarks of components used in this board.

- ARM is a registered trademark of ARM Limited.

- Android is a registered trademark of Google

- Linux is a registered trademark of Linus Torvalds.

- WinCE is a registered trademark of Microsoft

- TI is a registered trademark of Texas Instruments

- All other products and trademarks mentioned in this manual are trademarks of their respective owners.

### *Standards*

EMBEDIAN is ISO 9001:2008 and ISO14001-certified manufacturer. SMARC is an SGET standard for ARM computer on module.

### *Warranty*

This EMBEDIAN product is warranted against defects in material and workmanship for the warranty period from the date of shipment. During the warranty period, EMBEDIAN will at its discretion, decide to repair or replace defective products.

Within the warranty period, the repair of products is free of charge as long as warranty conditions are observed.

The warranty does not apply to defects resulting from improper or inadequate maintenance or handling by the buyer, unauthorized modification or misuse, operation outside of the product's environmental specifications or improper installation or maintenance.

## ***Embedian, Inc.***

EMBEDIAN will not be responsible for any defects or damages to other products not supplied by EMBEDIAN that are caused by a faulty EMBEDIAN product.

### ***Technical Support***

Technicians and engineers from EMBEDIAN and/or its subsidiaries and official distributors are available for technical support. We are committed to making our product easy to use and will help you use our products in your systems.

Before contacting EMBEDIAN technical support, please consult our Web site for the latest product documentation, utilities, and drivers. If the information does not help solve the problem, contact us by e-mail or telephone.

## Table of Contents

|                                                                                     |     |

|-------------------------------------------------------------------------------------|-----|

| <i>CHAPTER 1 INTRODUCTION</i> .....                                                 | 10  |

| <i>1.1 FEATURES AND FUNCTIONALITY</i> .....                                         | 10  |

| <i>1.2 MODULE VARIANT</i> .....                                                     | 12  |

| <i>1.3 BLOCK DIAGRAM</i> .....                                                      | 13  |

| <i>1.4 SOFTWARE SUPPORT / HARDWARE ABSTRACTION</i> .....                            | 14  |

| <i>1.5 DOCUMENT AND STANDARD REFERENCES</i> .....                                   | 14  |

| <i>CHAPTER 2 SPECIFICATIONS</i> .....                                               | 18  |

| <i>2.1 SMARC-FIMX6 GENERAL FUNCTIONS</i> .....                                      | 18  |

| <i>2.2 SMARC-FIMX6 DEBUG</i> .....                                                  | 94  |

| <i>2.3 MECHANICAL SPECIFICATIONS</i> .....                                          | 94  |

| <i>2.4 ELECTRICAL SPECIFICATIONS</i> .....                                          | 109 |

| <i>2.5 ENVIRONMENTAL SPECIFICATIONS</i> .....                                       | 114 |

| <i>CHAPTER 3 CONNECTOR PINOUT</i> .....                                             | 116 |

| <i>3.1 SMARC-FIMX6 CONNECTOR PIN MAPPING</i> .....                                  | 116 |

| <i>CHAPTER 4 POWER CONTROL SIGNALS BETWEEN SMARC-FIMX6 MODULE AND CARRIER</i> ..... | 147 |

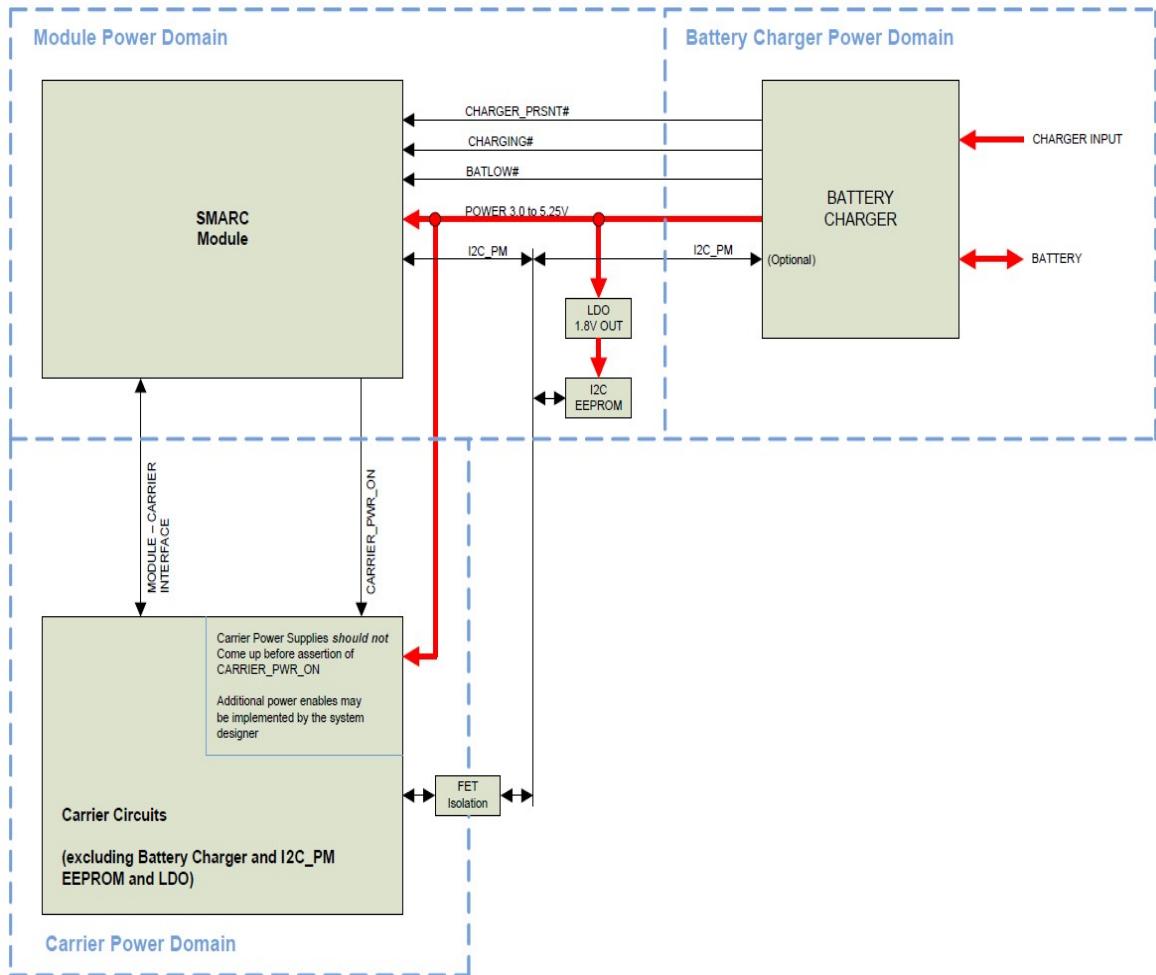

| <i>4.1 SMARC-FIMX6 MODULE POWER</i> .....                                           | 147 |

| <i>4.2 POWER SIGNALS</i> .....                                                      | 152 |

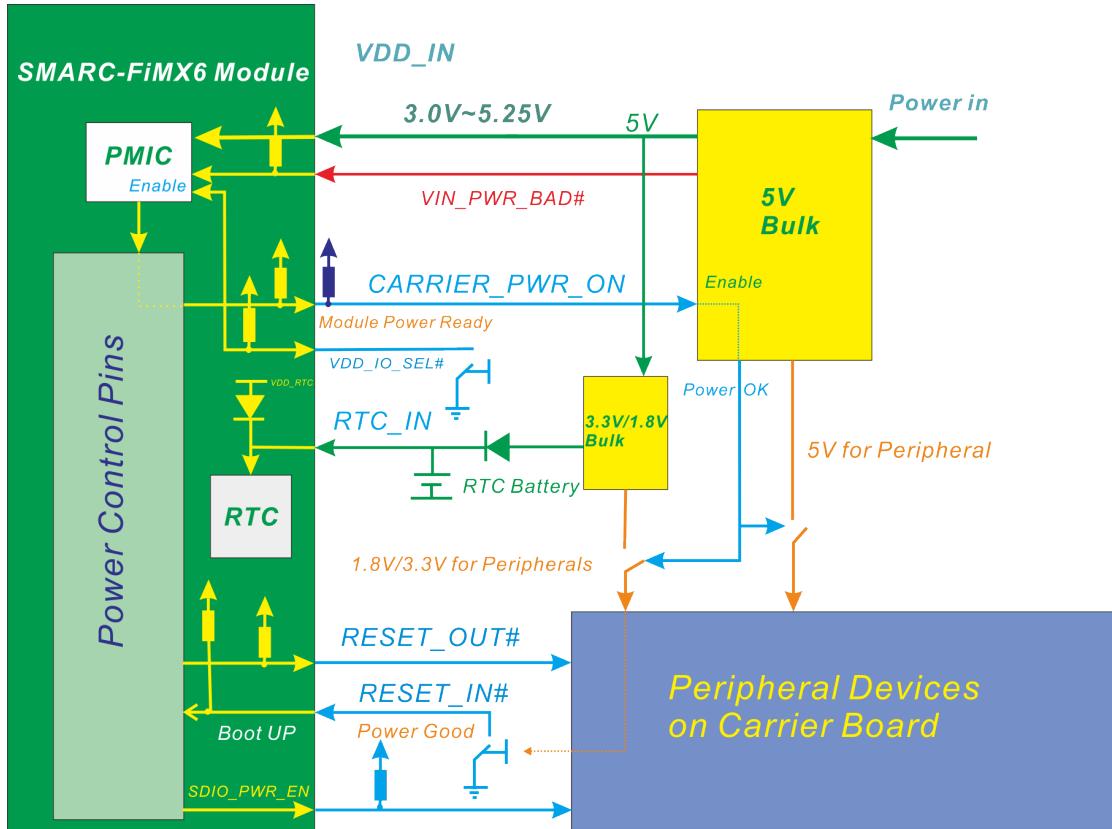

| <i>4.3 POWER FLOW AND CONTROL SIGNALS BLOCK DIAGRAM</i> .....                       | 156 |

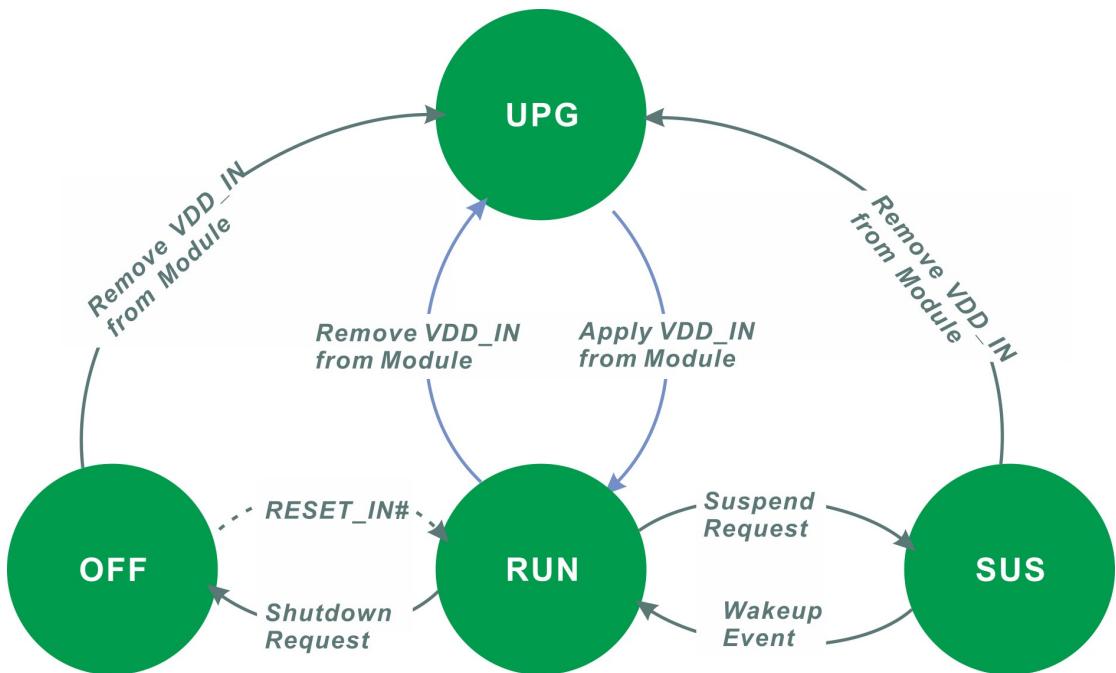

| <i>4.4 POWER STATES</i> .....                                                       | 158 |

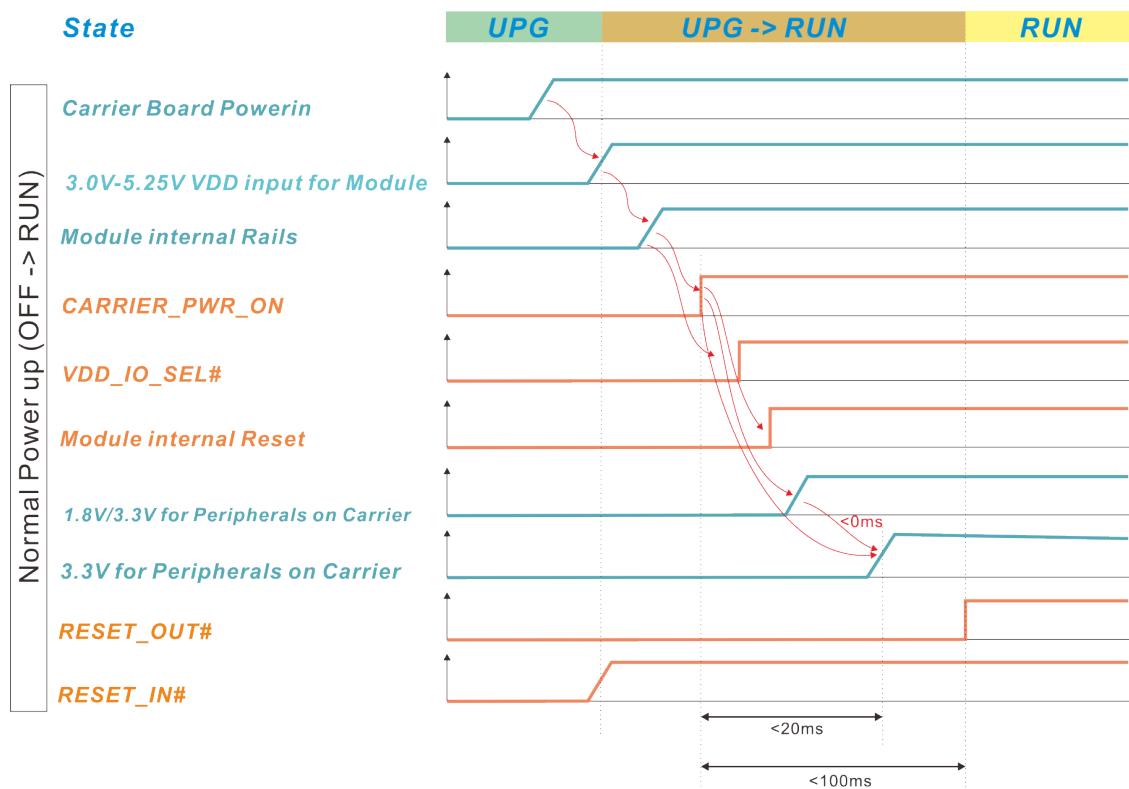

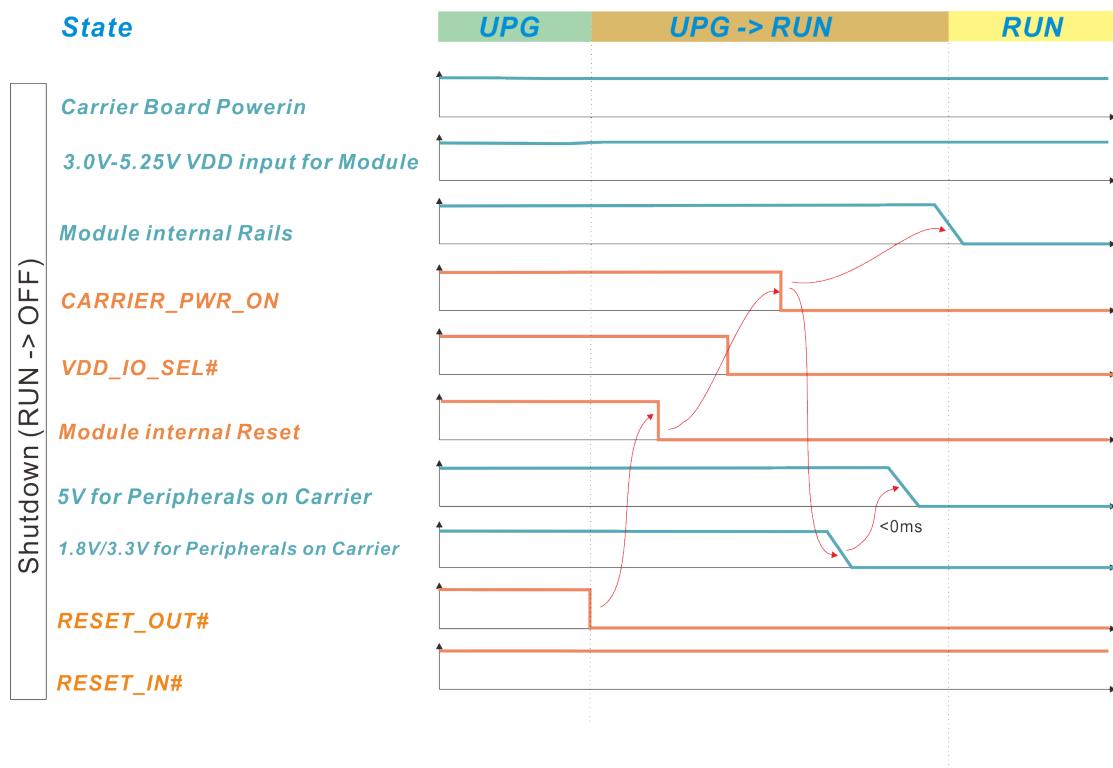

| <i>4.5 POWER SEQUENCES</i> .....                                                    | 159 |

| <i>4.6 TERMINATIONS</i> .....                                                       | 163 |

| <i>4.7 BOOT DEVICE SELECTION</i> .....                                              | 167 |

# Using this Manual

This guide provides information about the Embedian SMARC-FiMX6 for Freescale *i.MX6* embedded SMARC core module family.

## Conventions used in this guide

This table describes the typographic conventions used in this guide:

| <b>This Convention</b> | <b>Is used for</b>                                   |

|------------------------|------------------------------------------------------|

| <i>Italic</i> type     | Emphasis, new terms, variables, and document titles. |

| monospaced type        | Filenames, pathnames, and code examples.             |

## Embedian Information

### Document Updates

Please always check the product specific section on the Embedian support website at [www.embedian.com/](http://www.embedian.com/) for the most current revision of this document.

### Contact Information

For more information about your Embedian products, or for customer service and technical support, contact Embedian directly.

| <b>To contact Embedian by</b> | <b>Use</b>                                                              |

|-------------------------------|-------------------------------------------------------------------------|

| Mail                          | Embedian, Inc.<br>4F-7, 432 Keelung Rd. Sec. 1,<br>Taipei 11051, Taiwan |

| World Wide Web                | <a href="http://www.embedian.com/">http://www.embedian.com/</a>         |

| Telephone                     | + 886 2 2722 3291                                                       |

## Additional Resources

Please also refer to the most recent Freescale *i.MX6* processor reference

*Embeidian, Inc.*

manual and related documentation for additional information.

# Chapter

# 1

## Introduction

This Chapter gives background information on the

*SMARC-FiMX6*

Section include :

- Features and Functionality

- Module Variant

- Block diagram

- Software Support / Hardware Abstraction

- Module Variant

- Document and Standard References

# Chapter 1 Introduction

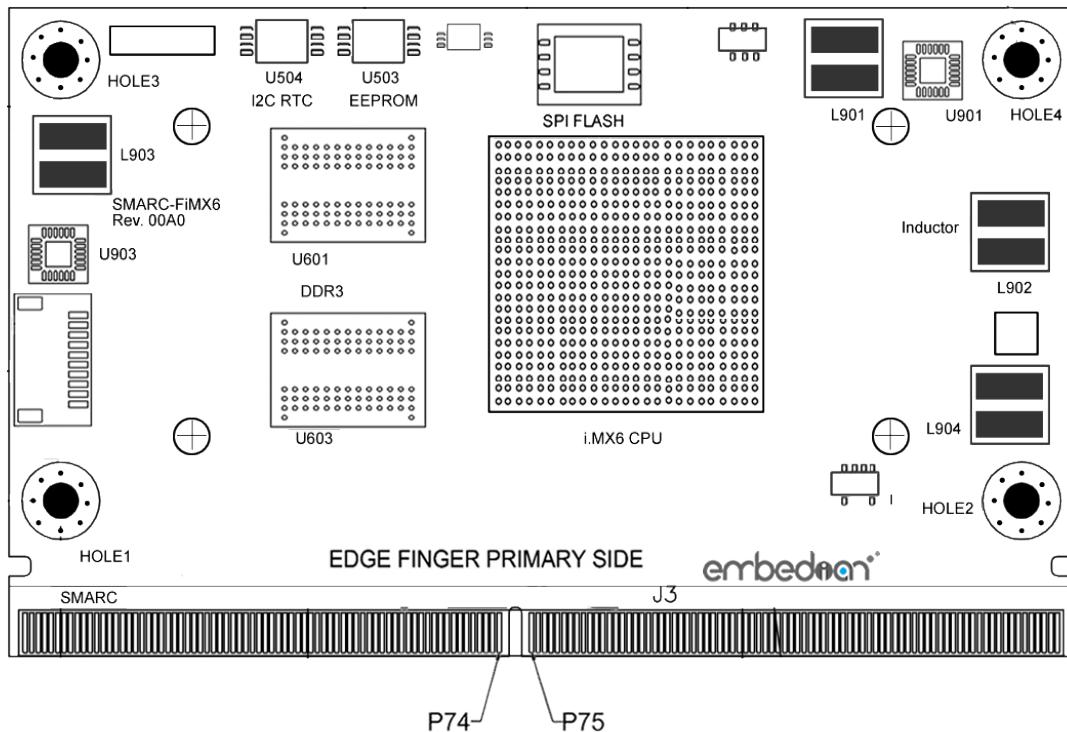

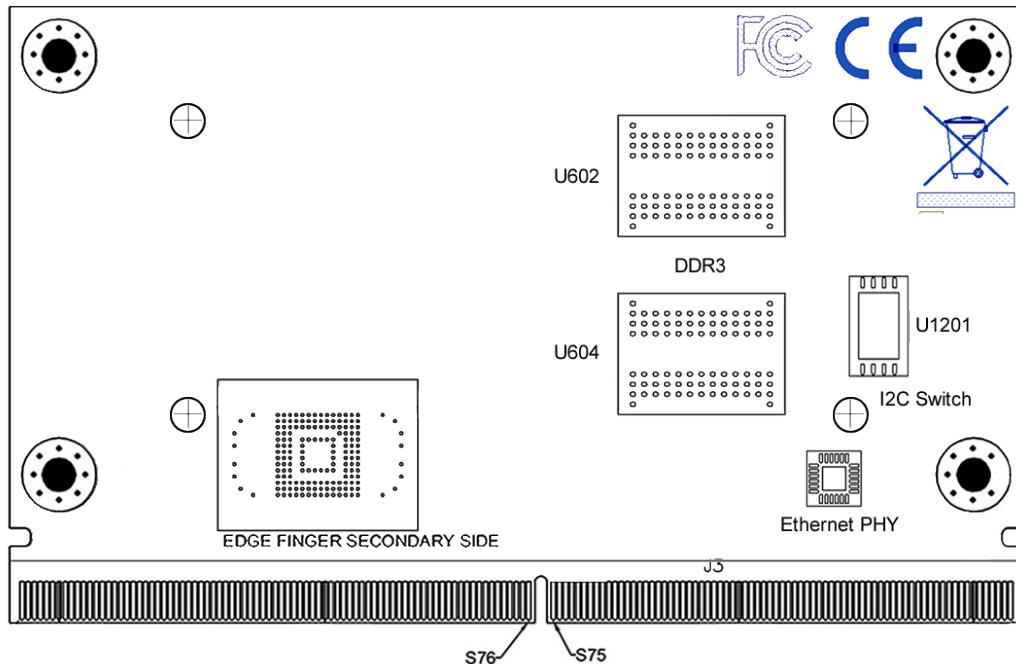

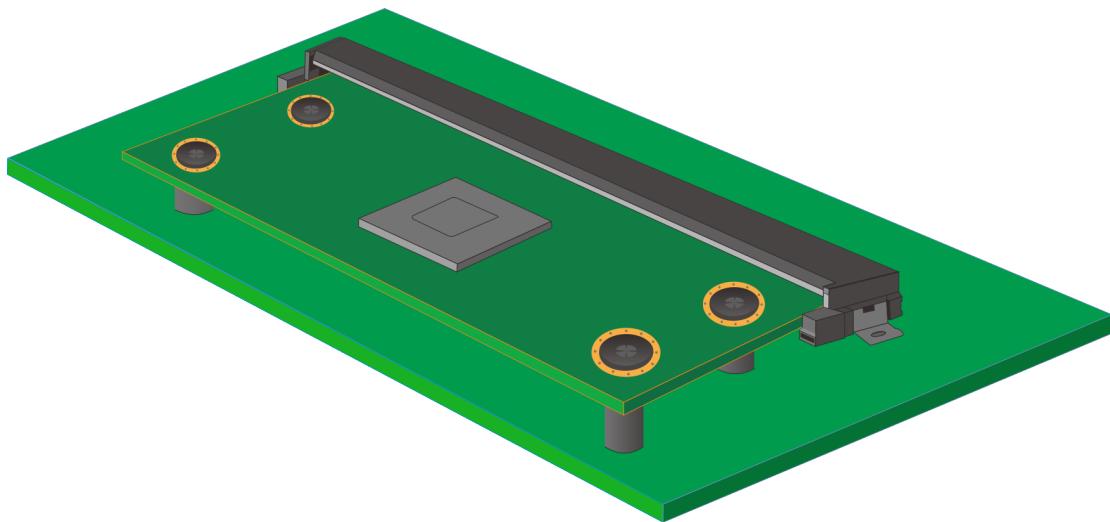

The **SMARC® (Smart Mobility ARChitecture) FiMX6** is a versatile small form factor Computer-On-Module with *Freescale i.MX6* processor and offers a wide range of processor scalability with single, dual and quadcore processors. The X86 alike interfacing of **SMARC-FiMX6** allows an easy integration in any kind of application.

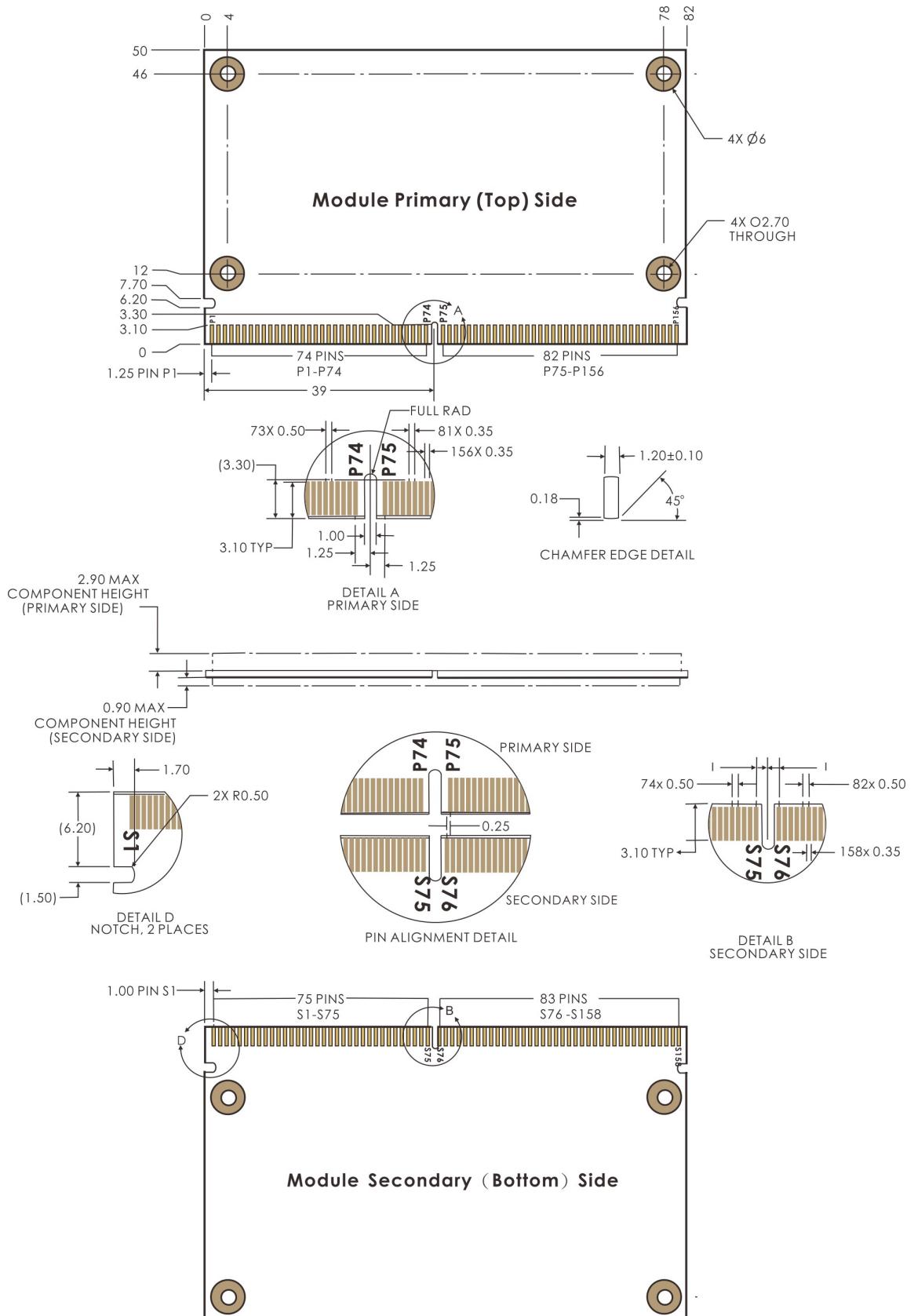

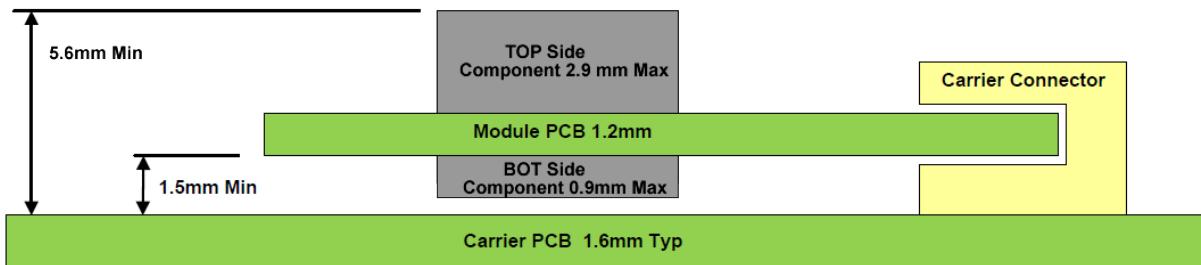

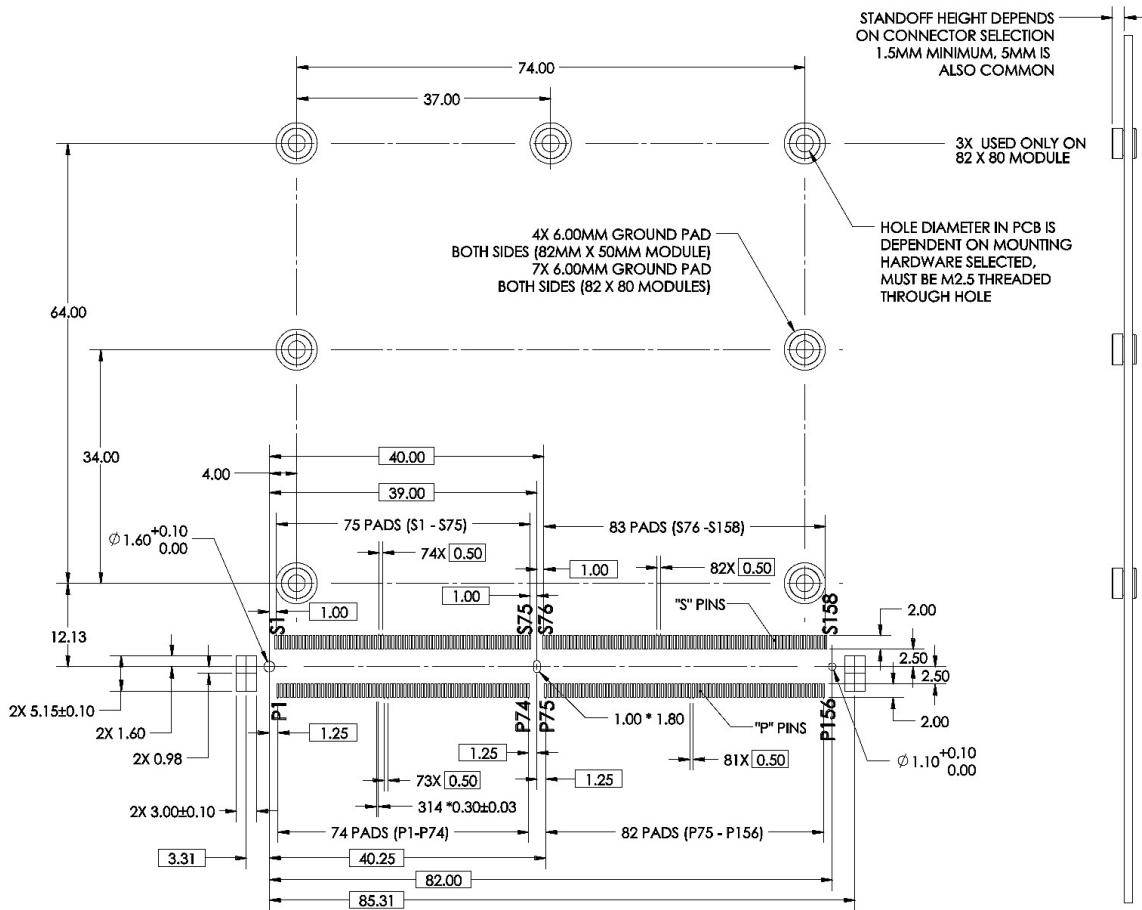

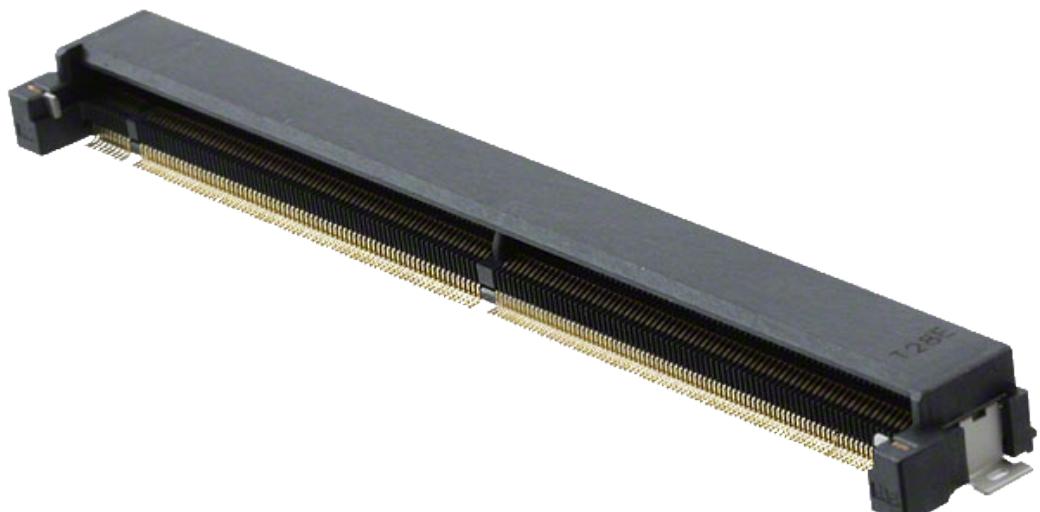

The module connector has 314 edge fingers that mate with a low profile 314 pin 0.5mm pitch right angle connector (this connector is sometimes identified as an 321 pin connector, but 7 pins are lost to the key).

Featuring *Freescale's i.MX6* System-on-Chip, Embedian's **SMARC-FiMX6** offers 24-bit Parallel LCD, single- or dual-channel LVDS, Gigabit Ethernet, HDMI, SDHC, USB 2.0, USB OTG, four UARTs support and many peripheral interfaces in a cost effective, low power, miniature package. Embedian's **SMARC-FiMX6** thin and robust design makes it an ideal building block for reliable system design.

The module is the ideal choice for a broad range of target markets including

- HVAC Building and Control Systems

- Rear seat and in-freight entertainment system.

- Smart Grid and Smart Metering

- Digital Signage

- HMI/ In-Home Display

- Smart Toll Systems

- Connected Vending Machines

- Display Unit

- General Control System

- And more

Complete and cost-efficient Embedian evaluation kits for Yocto, Ubuntu 12.04, Android ICS and Microsoft Windows Embedded Compact 7 allow immediate and professional embedded product development with dramatically reduced design risk and time-to-market.

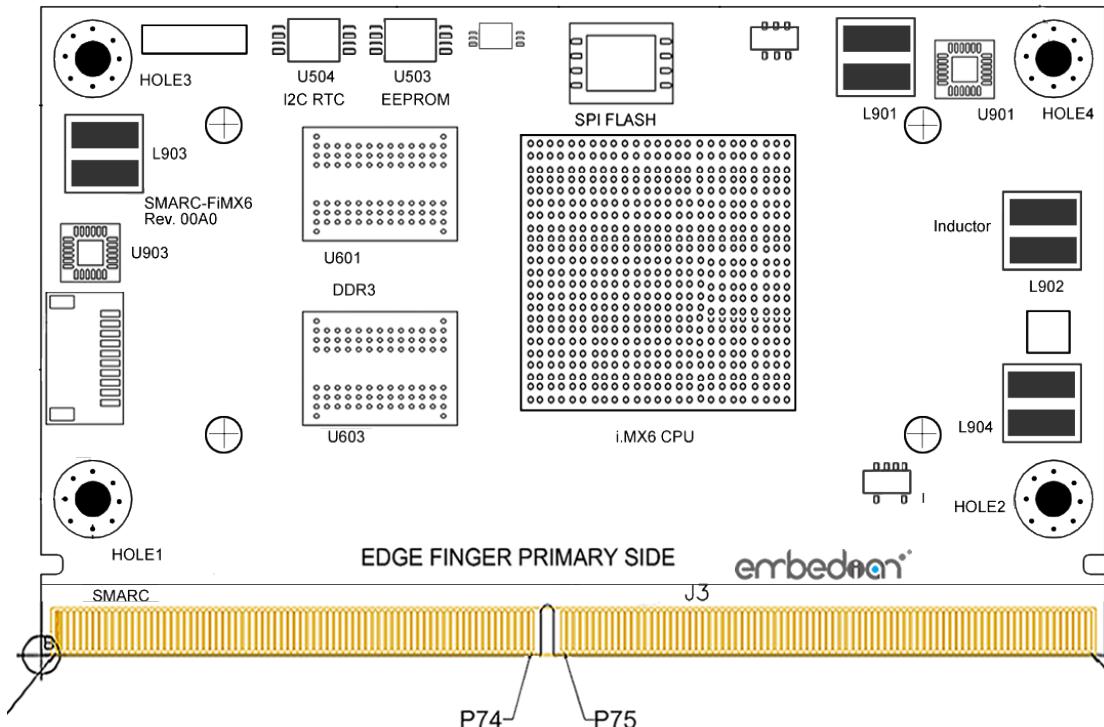

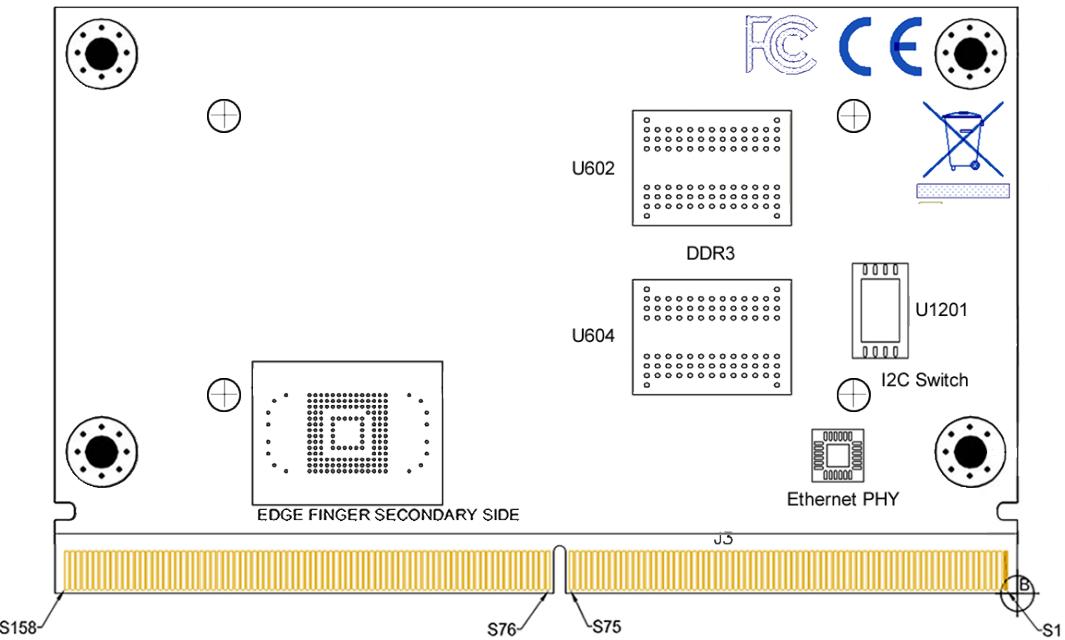

## 1.1 Features and Functionality

The **SMARC-FiMX** module is based on the *i.MX6* processor with solo, dual lite, dual and quad core from *Freescale*. This processor offers a high number of interfaces. The module has the following features:

- **SMARC 1.0 or 1.1** compliant in an 82mm x 50mm form factor.

- Processor: *Freescale i.MX6* ARM Cortex-A9 up to 1GHz

- Memory: Onboard 4GB eMMC Flash and 4MB SPI NOR Flash

- Onboard 1GB or 2GB DDR3 <sup>Note 1</sup>

- Networking: 1 x 10/100/1000 Mbps Ethernet

- Display: 24-bit Parallel LCD

- Single channel LVDS LCD 18 or 24 bit or dual channel LVDS

- HDMI

- Expansion: 2 x SDHC/SDIO, 1 x USB 2.0 Host

- USB: 1 x USB 2.0 Host, 1 x USB 2.0 OTG, 1 x PCIe

- A single 4KB EEPROM is provided on I2C0 that holds the board information. This information includes board name, serial number, and revision information.

- Additional Interface:

- ◆ 4 x UARTs

- ◆ 2 x SPI

- ◆ 4 x I2C

- ◆ 1 x I2S

- ◆ 2 x CAN Bus

- ◆ 1 x PWM

- ◆ 12 x GPIOs

- ◆ 1 x SATA (Dual and Quad only)

- ◆ WDT

- SW Support: Linux, Yocto, Ubuntu, Android ICS, Windows Embedded Compact 7

- Power Consumption (Typical)

- ◆ Solo Core (512MB DDR3): 1.55 Watts

- ◆ Dual Lite Core (1GB DDR3): 2.2 Watts

- ◆ Dual Core (1GB DDR3): 2.5 Watts

- ◆ Quad Core (1GB DDR3): 3.6 Watts

- Thermal:

- ◆ Normal Temperature: 0°C ~ 60°C

- ◆ Industrial Temperature: -40° ~85°C

- Power Supply

- 3V to 5.25V (single 5V is recommended in non-battery operation)

- 3.3V or 1.8V module IO support

**Note1:**

*SMARC-FiMX6-S* (solo core) only has 512MB DDR3 on board

*SMARC-FiMX6-U* (dual lite core) only has 1GB DDR3 memory on board (no 2GB option for this variant.)

## 1.2 Module Variant

The SMARC-FiMX6 module is available with various options based on processors in this family from Freescale, DDR3 memory configuration, voltage rail of VDDIO and operating temperature ranges.

- 1: “S” (solo core running up to 1GHz)

“U” (dual lite core running up to 1GHz)

“D” (dual core running up to 1GHz)

“Q” (quad core running up to 1GHz)

- 2: “1G” (1GB DDR3 memory)

“2G” (2GB DDR3 memory, only for dual and quad core)

3. “I” (Industrial temperature (-40°C~85°C), CPU running up to 800MHz)

Leave it Blank if normal temperature

For example, SMARC-FiMX-D-1G stands for dual core *i.MX6* processor running up to 1GHz with 1GB DDR3 memory in normal operating temperature.

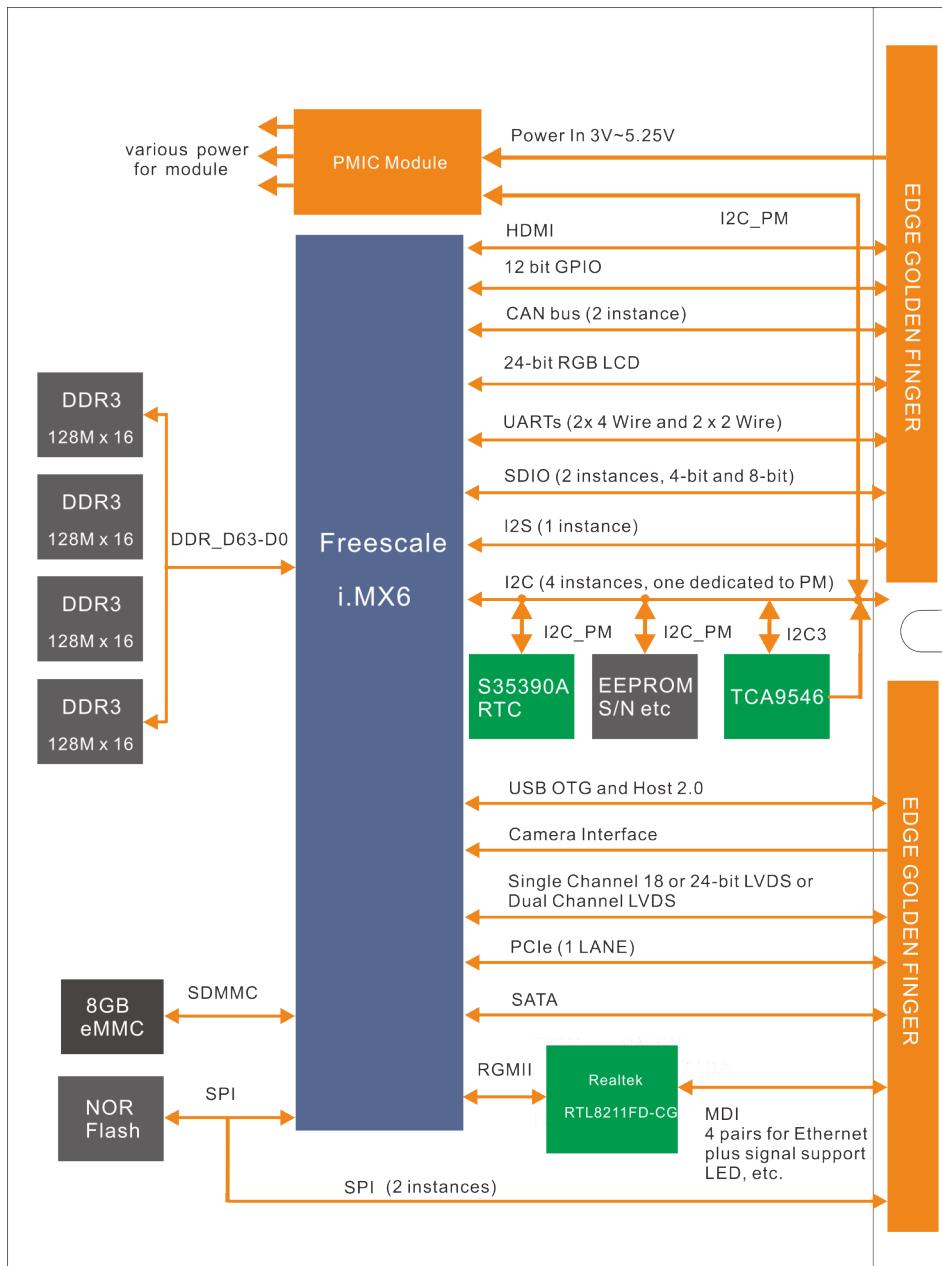

## 1.3 Block Diagram

The following diagram illustrates the system organization of the SMARC-FiMX6. Arrows indicate direction of control and not necessarily signal flow.

**Figure 1: SMARC-FiMX6 Block Diagram**

Details for this diagram will be explained in the following chapters.

## 1.4 Software Support / Hardware Abstraction

The Embedian *SMARC-FiMX6* Module is supported by Embedian BSPs (Board Support Package). The first *SMARC-FiMX6* BSP targets Linux (Ubuntu 14.04 LTS and Yocto Project) and Android support. BSPs for other operating systems are planned. Check with your Embedian contact for the latest BSPs. This manual goes into a lot of detail on I/O particulars – information is provided on exactly how the various *SMARC* edge fingers tie into the Freescale i.MX6 SoC and to other Module hardware. This is provided for reference and context. Almost all of the I/O particulars are covered and abstracted in the BSP and it should generally not be necessary for users to deal with I/O at the register level.

## 1.5 Document and Standard References

### 1.5.1. External Industry Standard Documents

- **eMMC (Embedded Multi-Media Card)** the eMMC electrical standard is defined by JEDEC JESD84-B45 and the mechanical standard by JESD84-C44 ([www.jedec.org](http://www.jedec.org)).

- **The I2C Specification**, Version 2.1, January 2000, Philips Semiconductor (now NXP) ([www.nxp.com](http://www.nxp.com)).

- **I2S Bus Specification**, Feb. 1986 and Revised June 5, 1996, Philips Semiconductor (now NXP) ([www.nxp.com](http://www.nxp.com)).

- **JTAG (Joint Test Action Group** defined by IEEE 1149.1-2001 - IEEE Standard Test Access Port and Boundary Scan Architecture ([www.ieee.org](http://www.ieee.org)).

- **MXM3 Graphics Module Mobile PCI Express Module Electromechanical Specification**, Version 3.0, Revision 1.1, © 2009 NVIDIA Corporation ([www.mxm-sig.org](http://www.mxm-sig.org)).

- **PICMG® EEEP Embedded EEPROM Specification**, Rev. 1.0, August 2010 ([www.picmg.org](http://www.picmg.org)).

- **SD Specifications Part 1 Physical Layer Simplified Specification**, Version 3.01, May 18, 2010, © 2010 SD Group and SD Card Association (Secure Digital) ([www.sdcard.org](http://www.sdcard.org)).

- **SPI Bus** – “Serial Peripheral Interface” - de-facto serial interface standard defined by Motorola. A good description may be found on Wikipedia ([http://en.wikipedia.org/wiki/Serial\\_Peripheral\\_Interface\\_Bus](http://en.wikipedia.org/wiki/Serial_Peripheral_Interface_Bus)).

- **USB Specifications** ([www.usb.org](http://www.usb.org)).

- **Serial ATA Revision 3.1**, July 18, 2011, Gold Revision, © Serial ATA

International Organization ([www.sata-io.org](http://www.sata-io.org))

- **PCI Express Specifications** ([www.pci-sig.org](http://www.pci-sig.org))

- **SPDIF (aka S/PDIF) ("Sony Philips Digital Interface)- IEC 60958-3**

-

#### **1.5.2. SGET Documents**

- **SMARC\_Hardware\_Specification\_V1p0**, version 1.0, December 20, 2012.

- **SMARC\_Hardware\_Specification\_V1p1**, version 1.1, May 29, 2014.

- **Smart Mobility Architecture Design Guide**, version 1.0, July 9, 2013

- **Smart Mobility Architecture Design Guide**, version 1.1, May 29, 2014

#### **1.5.3. Embedian Documents**

The following documents are listed for reference. The Module schematic is not usually available outside of Embedian, without special permission. The other schematics will be available. Contact your Embedian representative for more information. The SMARC Evaluation Carrier Board Schematic is particularly useful as an example of the implementation of various interfaces on a Carrier board.

- **SMARC Evaluation Carrier Board Schematic**, PDF and OrCAD format

- **SMARC Evaluation Carrier Board User's Manual**

- **SMARC-FIMX6 User's Manual**

- **SMARC-FIMX6 Schematic Checklist**

#### **1.5.4. Freescale Documents**

- **IMX6DQRM, i.MX 6Dual/6Quad Applications Processor Reference Manual**, May 2014 (rev. 2)

- **IMX6DQ6SDLHDG, Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors**, June 2013 (rev. 1)

- **AN4059, i.MX 6Dual/6Quad Power Consumption Measurement**, Oct 2012 (rev. 0)

#### 1.5.5. Freescale Development Tools

- ***IOMUX\_TOOL* for ARM® i.MX6 Microprocessors**

- ***IMX\_CST\_TOOL***, Freescale Code Signing Tool for the High Assurance Boot library.

#### 1.5.6. Freescale Software Documents

- ***L3.0.101\_SOURCE\_BSP***, i.MX 6Quad, i.MX 6Dual, i.MX 6DualLite, i.MX 6Solo and i.MX 6Sololite Linux BSP Source Code Files. Nov 3, 2014 (Rev.# L3.0.101)

- ***Fsl-L3.10.17\_1.0.2\_iMX6QDLS\_BUNDLE***, i.MX 6Quad, i.MX 6Dual, i.MX 6DualLite, i.MX 6Solo Linux Binary Demo Files and Linux BSP Documentation. Oct. 29, 2014 (Rev.# L3.10.17)

- ***IMX6\_JB43\_110\_ANDROID\_SOURCE\_BSP***, i.MX 6Quad, i.MX 6Dual, i.MX 6DualLite, i.MX 6Solo and i.MX 6Sololite Android jb4.3\_1.1.0 0 BSP, Documentation and Source Code for BSP and Codecs. Dec. 19, 2013 (Rev.# jb4.3\_1.1.0)

- ***IMX6\_KK442\_100\_ANDROID\_SOURCE\_BSP***, i.MX 6Quad, i.MX 6Dual, i.MX 6DualLite, i.MX 6Solo and i.MX 6Sololite Android KK4.4.2\_1.0.0 BSP, Source Code for BSP and Codecs. July 14, 2014 (Rev.# KK442.2\_1.0.0)

#### 1.5.7. Embedian Software Documents

- ***Embedian Linux BSP for SMARC-FiMX6 Module***

- ***Embedian Android BSP for SMARC-FiMX6 Module***

- ***Embedian Linux BSP User's Guide***

- ***Embedian Android BSP User's Guide***

#### 1.5.8. Freescale Design Network

- ***SABRE***

- ***Wandboard***

- ***Nucleus***

- ***QNX***

# Chapter

# 2

## Specifications

This Chapter provides SMARC-FiMX6 specifications.

Section include :

- SMARC-FiMX6 General Functions

- SMARC-FiMX6 Debug

- Mechanical Specifications

- Electrical Specification

- Environment Specification

# Chapter 2 Specifications

## 2.1 SMARC-FiMX6 General Functions

### 2.1.1. SMARC-FiMX6 Feature Set

This section lists the complete feature set supported by the *SMARC-FiMX6* module.

| SMARC Feature Specification                     | SMARC Specification Maximum Number Possible | SMARC-FiMX6 Feature Support | SMARC-FiMX6 Feature Support Instances |

|-------------------------------------------------|---------------------------------------------|-----------------------------|---------------------------------------|

| <i>LVDS Display Support</i>                     | 1                                           | Yes                         | 1 (18 or 24 bits) <sup>Note1</sup>    |

| <i>Parallel LCD Support</i>                     | 1                                           | Yes                         | 1 (24 bits)                           |

| <i>HDMI Display Support</i>                     | 1                                           | Yes                         | 1                                     |

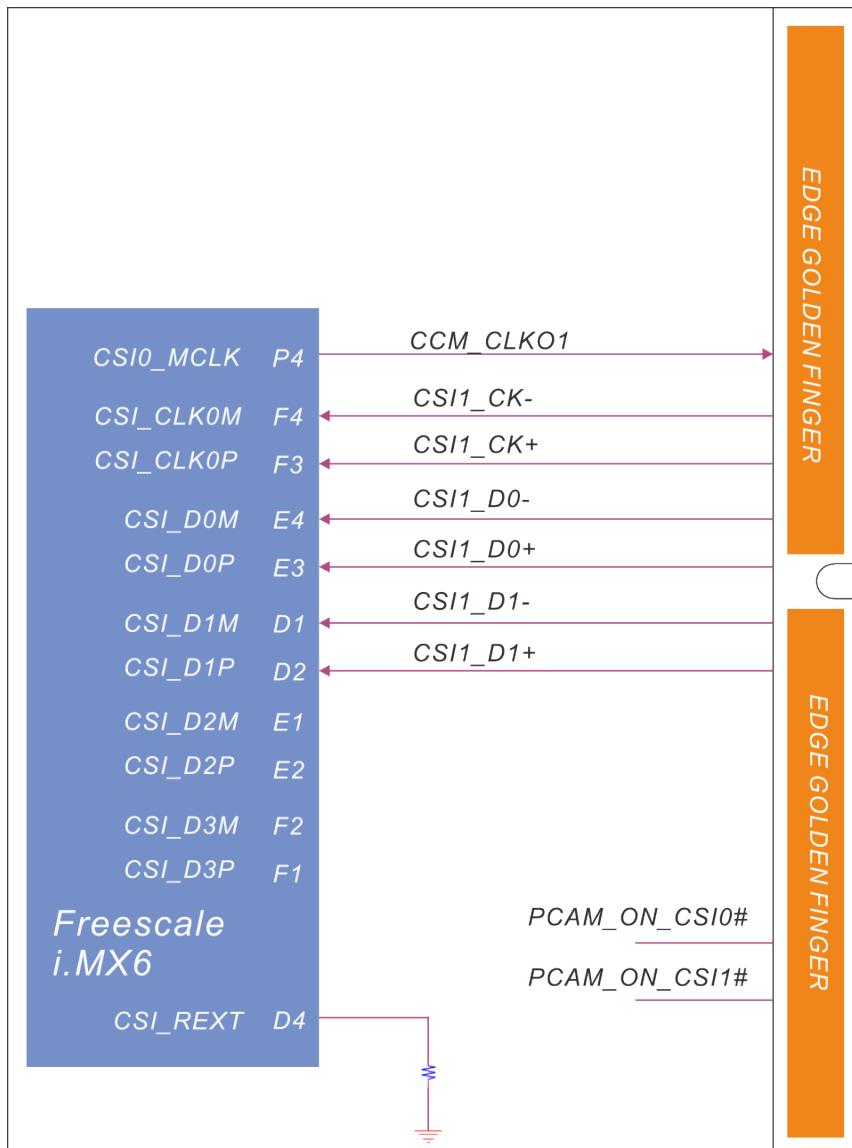

| <i>CSI Camera Support (Dual and Quad lanes)</i> | 2                                           | Yes                         | 1 (Quad Lane)                         |

| <i>Serial Camera Support</i>                    | 2                                           | Yes                         | 1 (4 lanes)                           |

| <i>USB Interface</i>                            | 3                                           | Yes                         | 2                                     |

| <i>PCIe Interface</i>                           | 3                                           | Yes                         | 1 (one Lane)                          |

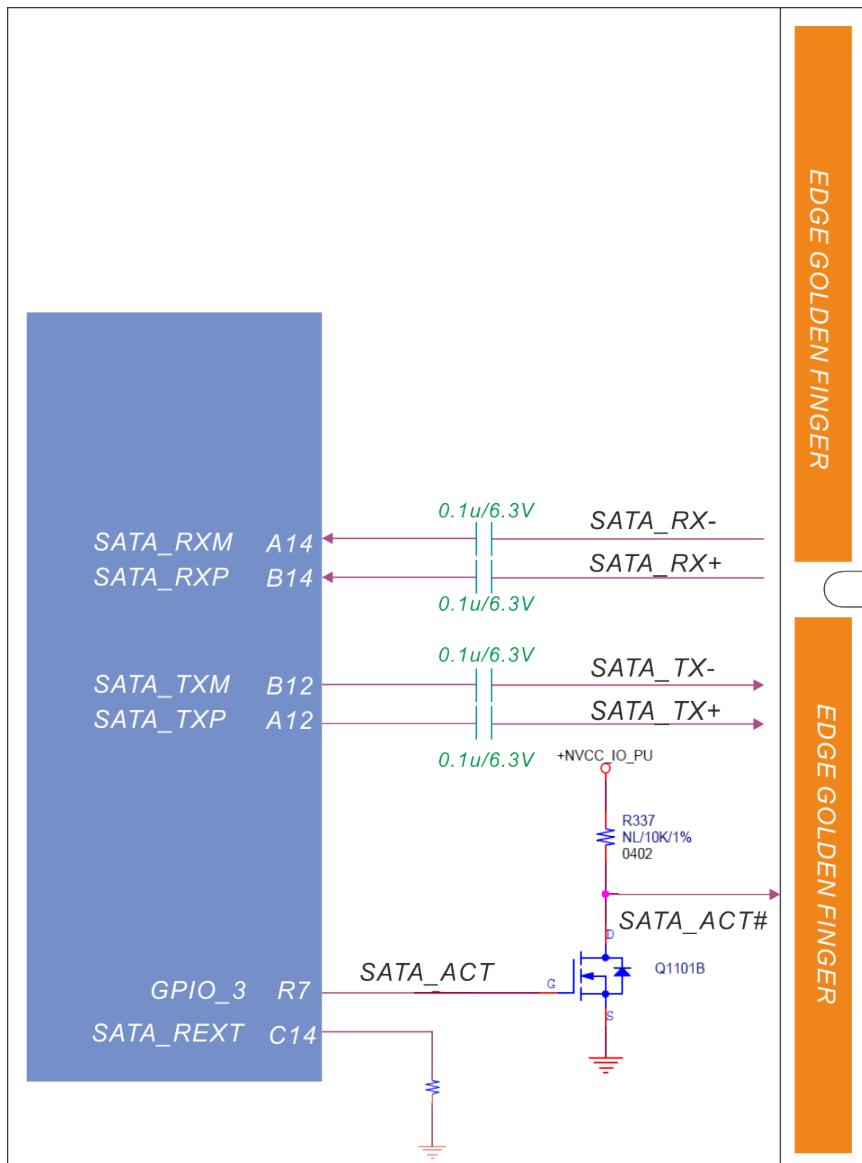

| <i>SATA Interface</i>                           | 1                                           | Yes                         | 1 (0 on Solo and DualLite)            |

| <i>GbE Interface</i>                            | 1                                           | Yes                         | 1                                     |

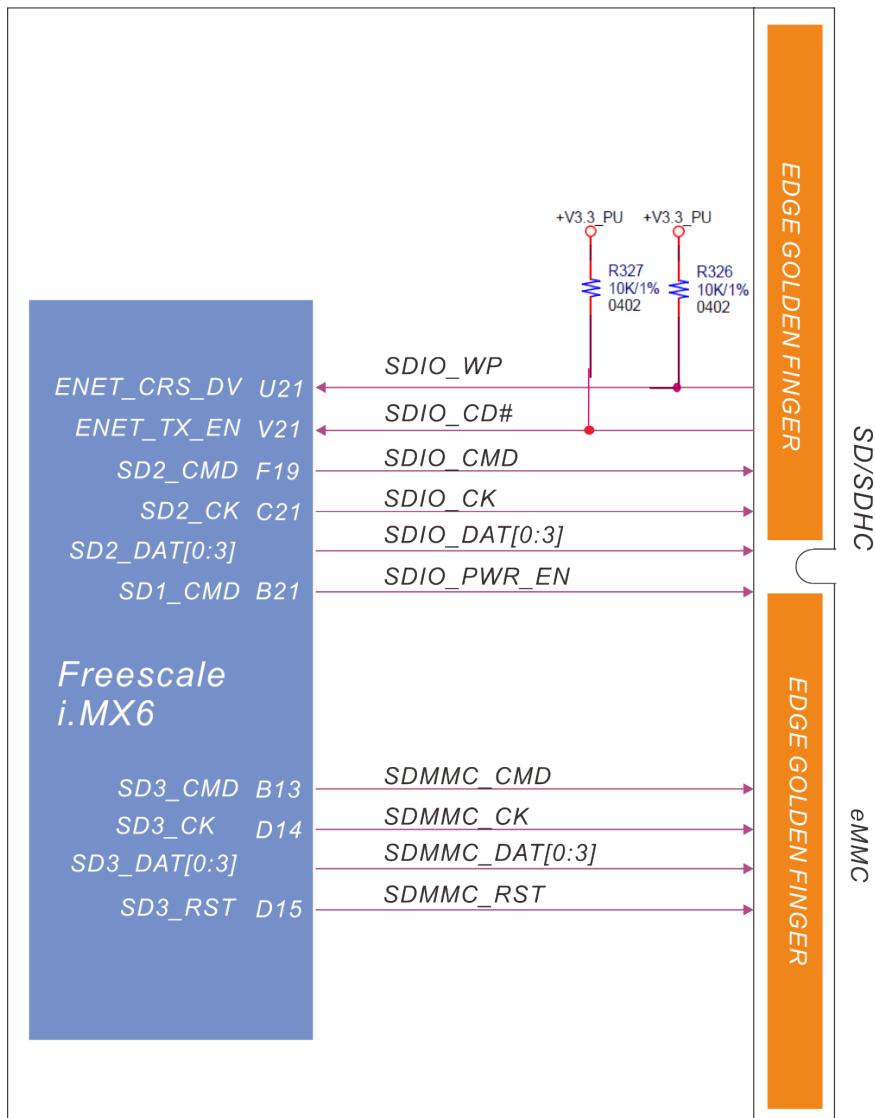

| <i>SDIO Interface (4bit)</i>                    | 1                                           | Yes                         | 1 (max. 25MHz)                        |

| <i>SDMMC Interface (8bit)</i>                   | 1                                           | Yes                         | 1 (max. 25MHz)                        |

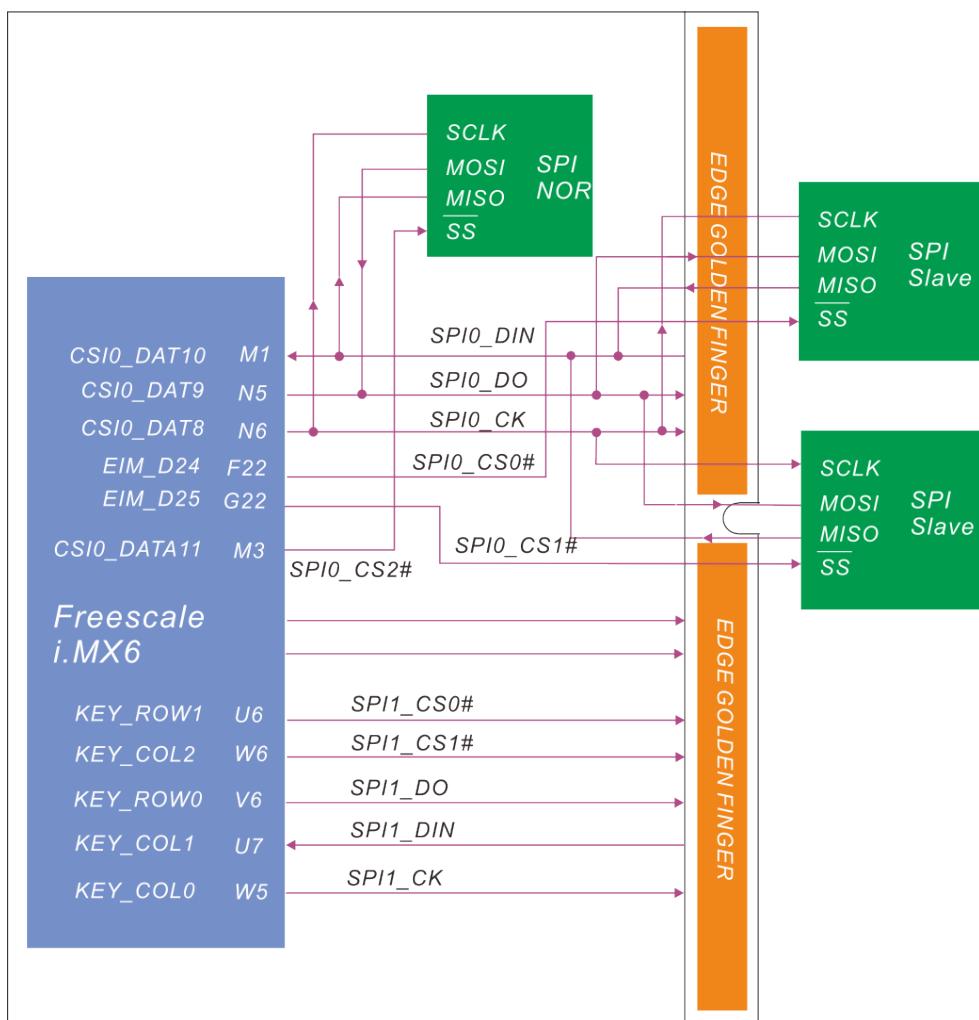

| <i>SPI Interface</i>                            | 2                                           | Yes                         | 2                                     |

| <i>I2S Interface</i>                            | 3                                           | Yes                         | 1                                     |

| <i>I2C Interface</i>                            | 5                                           | Yes                         | 5                                     |

| <i>Serial</i>                                   | 4                                           | Yes                         | 4                                     |

| <i>CAN</i>                                      | 2                                           | Yes                         | 2                                     |

| SMARC Feature Specification             | SMARC Specification Maximum Number Possible | SMARC-FiMX6 Feature Support | SMARC-FiMX6 Feature Support Instances                |

|-----------------------------------------|---------------------------------------------|-----------------------------|------------------------------------------------------|

| <b>AFB</b>                              |                                             | Yes                         | <i>Dual Channel LVDS is realized<sup>Note2</sup></i> |

| <b>I/O Voltage (1.8V) Level Support</b> |                                             | Yes                         |                                                      |

| <b>I/O Voltage (3.3V) Level Support</b> |                                             | Yes                         |                                                      |

**Note:**

1. Single channel LVDS interface: 1 x 18 bpp OR 1 x 24 bpp (up to 85 MHz per interface e.g 1366x768 @ 60Hz + 35% blanking)

2. Dual channel LVDS interface: 2 x 18 bpp OR 2 x 24 bpp (up to 170 MHz pixel clock e.g 1600x1200 @ 60 Hz + 35% blanking).

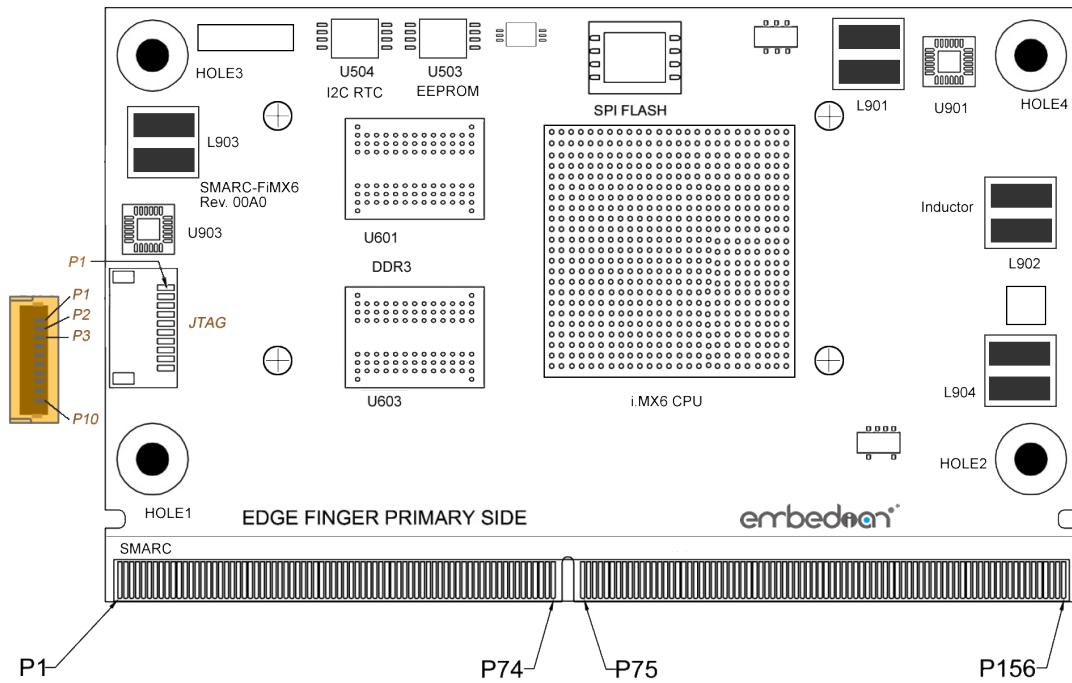

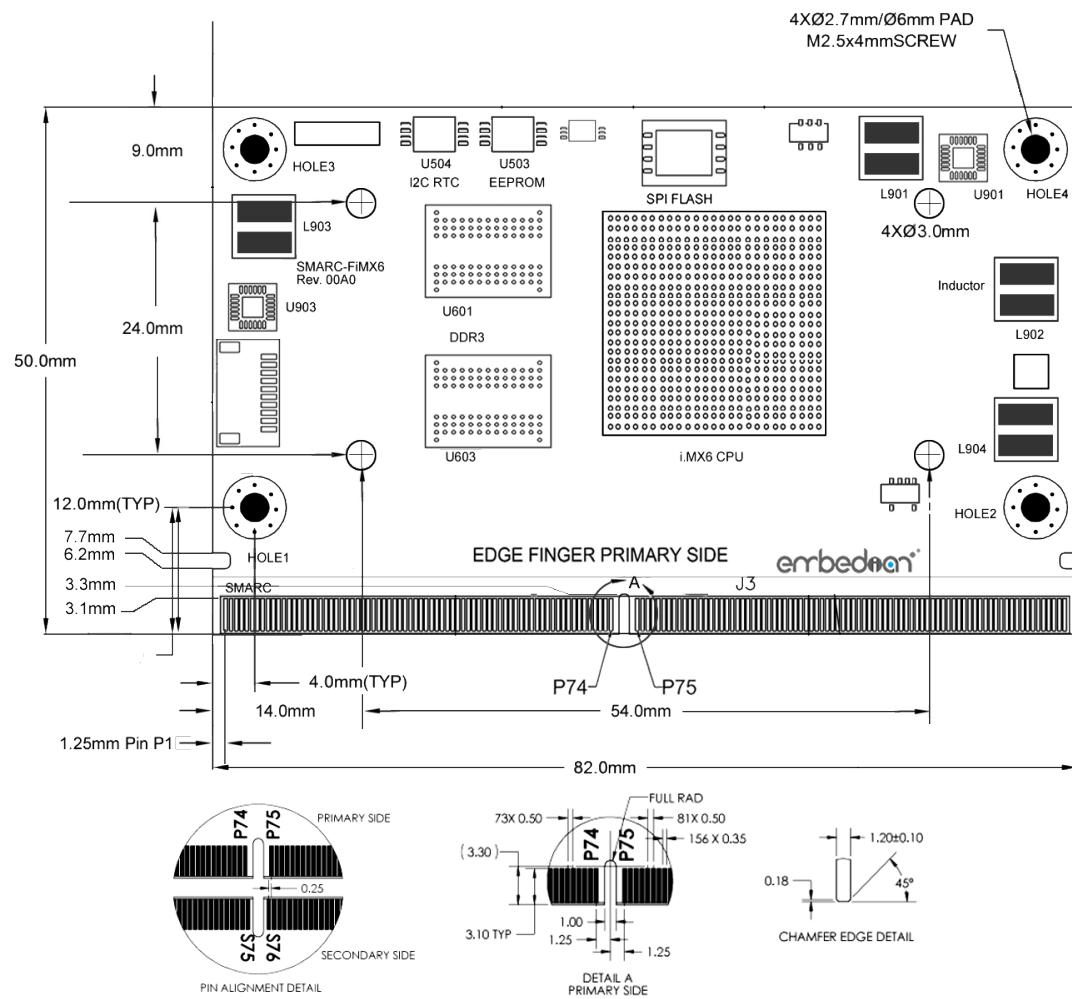

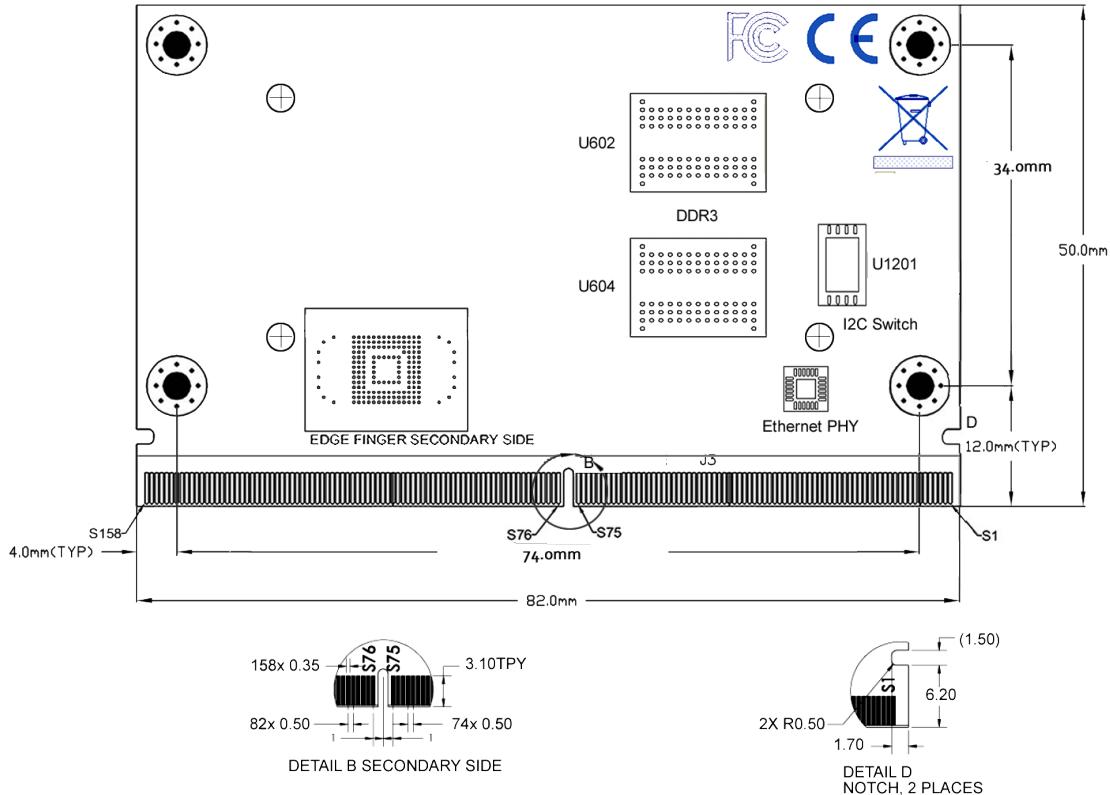

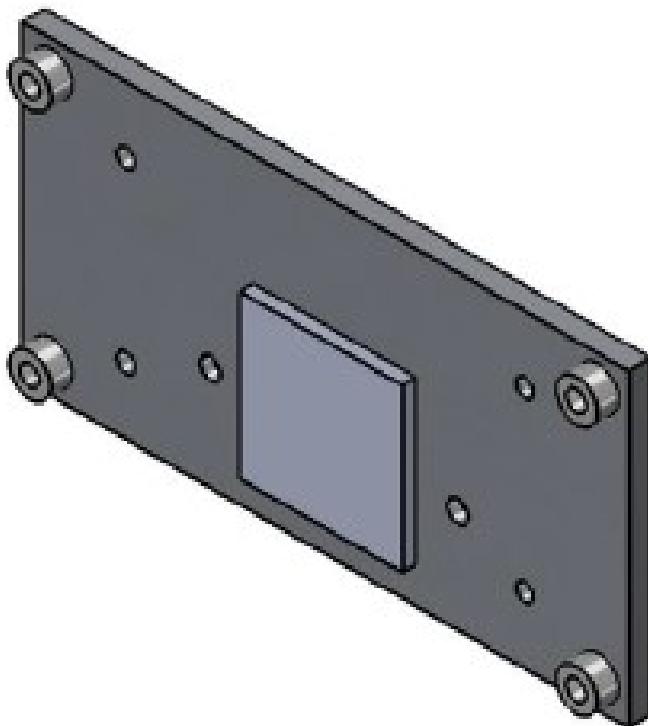

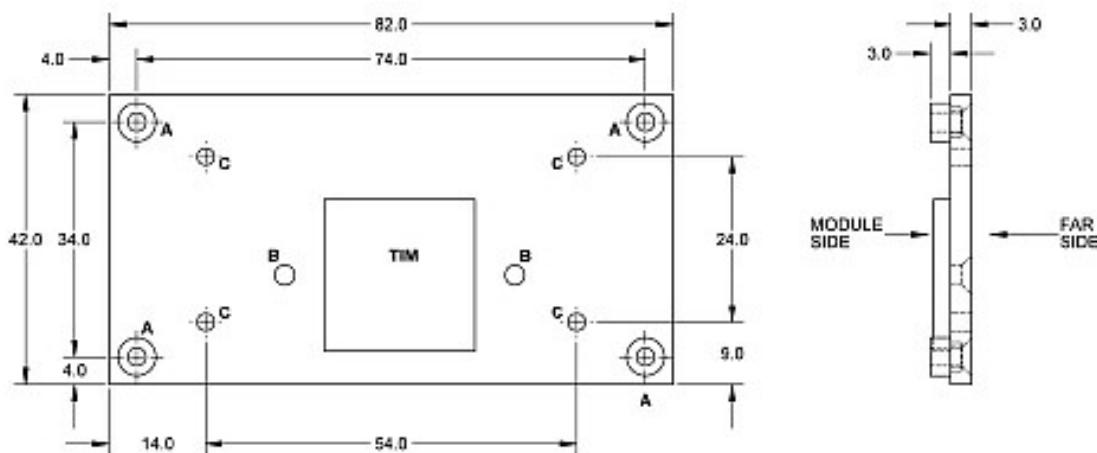

### 2.1.2. Form Factor

The SMARC-FiMX6 module complies with the SMARC General Specification module size requirements in an 82mm x 50mm form factor.

### 2.1.3. CPU

The SMARC-FiMX6 implements Freescale's *i.MX6* ARM processor.

| <b>Freescale CPU</b>            | <i>i.MX6 Solo</i>                                                                                                        | <i>i.MX6 DualLite</i>                                                                                                    | <i>i.MX6 Dual</i>                                                                                                        | <i>i.MX6 Quad</i>                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| <b>Cores</b>                    | 1                                                                                                                        | 2                                                                                                                        | 2                                                                                                                        | 4                                                                                                                        |

| <b>Clock<sup>Note1</sup></b>    | 1GHz                                                                                                                     | 1GHz                                                                                                                     | 1GHz                                                                                                                     | 1GHz                                                                                                                     |

| <b>Memory Speed</b>             | DDR3-400                                                                                                                 | DDR3-400                                                                                                                 | DDR3-533                                                                                                                 | DDR3-533                                                                                                                 |

| <b>Memory Bus</b>               | 32-bit                                                                                                                   | 64-bit                                                                                                                   | 64-bit                                                                                                                   | 64-bit                                                                                                                   |

| <b>Cache</b>                    | 512KB L2                                                                                                                 | 512KB L2                                                                                                                 | 1MB L2 + VFPv3                                                                                                           | 1MB L2 + VFPv3                                                                                                           |

| <b>GFX</b>                      | Vivante                                                                                                                  | Vivante                                                                                                                  | Vivante                                                                                                                  | Vivante                                                                                                                  |

| <b>GFX core frequency</b>       | 528MHz                                                                                                                   | 528MHz                                                                                                                   | 528MHz                                                                                                                   | 528MHz                                                                                                                   |

| <b>IPUs</b>                     | 1                                                                                                                        | 1                                                                                                                        | 2                                                                                                                        | 2                                                                                                                        |

| <b>LVDS</b>                     | Single or Dual Channel (18-bit or 24-bit)                                                                                |

| <b>LVDS Resolutions</b>         | Single channel LVDS interface : 1 x 18 bpp or 1 x 24 bpp (up to 85 MHz per interface e.g 1366x768 @ 60Hz + 35% blanking) | Single channel LVDS interface : 1 x 18 bpp or 1 x 24 bpp (up to 85 MHz per interface e.g 1366x768 @ 60Hz + 35% blanking) | Single channel LVDS interface : 1 x 18 bpp or 1 x 24 bpp (up to 85 MHz per interface e.g 1366x768 @ 60Hz + 35% blanking) | Single channel LVDS interface : 1 x 18 bpp or 1 x 24 bpp (up to 85 MHz per interface e.g 1366x768 @ 60Hz + 35% blanking) |

|                                 | Dual channel LVDS interface: 2 x 18 bpp OR 2 x 24 bpp (up to 170 MHz pixel clock e.g 1600x1200 @ 60 Hz + 35% blanking).  | Dual channel LVDS interface: 2 x 18 bpp OR 2 x 24 bpp (up to 170 MHz pixel clock e.g 1600x1200 @ 60 Hz + 35% blanking)   | Dual channel LVDS interface: 2 x 18 bpp OR 2 x 24 bpp (up to 170 MHz pixel clock e.g 1600x1200 @ 60 Hz + 35% blanking)   | Dual channel LVDS interface: 2 x 18 bpp OR 2 x 24 bpp (up to 170 MHz pixel clock e.g 1600x1200 @ 60 Hz + 35% blanking)   |

| <b>Parallel LCD Resolutions</b> | 1920x1080x60                                                                                                             | 1920x1080x60                                                                                                             | 1920x1080x60                                                                                                             | 1920x1080x60                                                                                                             |

| <b>HDMI Resolutions</b>         | 1920x1080x60                                                                                                             | 1920x1080x60                                                                                                             | 1920x1200x60                                                                                                             | 1920x1200x60                                                                                                             |

| <b>Freescale CPU</b>                       | <i>i.MX6 Solo</i> | <i>i.MX6 DualLite</i> | <i>i.MX6 Dual</i> | <i>i.MX6 Quad</i> |

|--------------------------------------------|-------------------|-----------------------|-------------------|-------------------|

| <b>3D Graphics</b>                         | 1 shader          | 1 shader              | 4 shaders         | 4 shaders         |

| <b>2D Graphics</b>                         | X1                | X1                    | X2                | X2                |

| <b>Independent Display<sup>Note2</sup></b> | -                 | -                     | yes               | yes               |

**Note:**

1. For industrial temp. boards, the clocking speed is only up to 800MHz.

2. The LVDS interface can be used either as a single channel or as a dual channel. It is also possible to use the LVDS interface as two independent single LVDS channels. To do this, it is recommended to configure the LVDS display in the bootloader. Three independent displays are possible when connected as two single LVDS channel and one HDMI interface.

#### 2.1.4. Module Memory

The SMARC-FiMX6 module supports different configurations of DDR3 memory. The following table shows the available options.

| <b>SMARC Variants</b> | <i>i.MX6 Solo</i> | <i>i.MX6 DualLite</i> | <i>i.MX6 Dual</i> | <i>i.MX6 Quad</i> |

|-----------------------|-------------------|-----------------------|-------------------|-------------------|

| <b>512MB DDR3</b>     | Yes               | No                    | No                | No                |

| <b>1GB DDR3</b>       | No                | Yes                   | Yes               | Yes               |

| <b>2GB DDR3</b>       | No                | No                    | Yes               | Yes               |

Check with your Embedian contact or on the Embedian web site for updated information.

### 2.1.5. Graphic Core

The integrated Vivante core based supports:

|                                   |                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3D Graphic Core</b>            | Vivante GC2000                                                                                                                                                                                                                                                                                                                       |

| <b>Shader Cores</b>               | <p><i>Solo: 1 Core</i></p> <p><i>Dual Lite: 1 Core</i></p> <p><i>Dual: 4 Cores</i></p> <p><i>Quad: 4 Cores</i></p>                                                                                                                                                                                                                   |

| <b>2D Core</b>                    | Vivante GC320                                                                                                                                                                                                                                                                                                                        |

| <b>2D Performance</b>             | 633M pixels / sec raw performance                                                                                                                                                                                                                                                                                                    |

| <b>Vector Graphics Core</b>       | Vivante GC355                                                                                                                                                                                                                                                                                                                        |

| <b>API (DirectX/OpenGL)</b>       | OpenGL ES 1.1/2.0/3.0, OpenCL 1.1 EP, OpenVG 1.1                                                                                                                                                                                                                                                                                     |

| <b>Hardware Accelerated Video</b> | <p><i>Encode:</i></p> <p>H.264 BP/CBP</p> <p>H.263 V2</p> <p>MPEG-4 SP</p> <p>MPEG-2</p> <p>MJPEG Baseline</p> <p><i>Decode:</i></p> <p>MPEG2 MP/HP</p> <p>MPEG4/Xvid SP/ASP</p> <p>H.264 BP/MP/HP</p> <p>H.264 MVC BP/MP/HP</p> <p>H.263 V2</p> <p>DivX v3/4/5/6</p> <p>VC-1 SP/MP/AP</p> <p>MJPEG Baseline</p> <p>VP6/VebM VP8</p> |

### 2.1.6. Onboard Storage

The SMARC-FiMX6 module supports a 4GB eMMC flash memory device, 4MB SPI NOR flash and a 32Kb I2C serial EEPROM on the Module I2C\_PM (I2C0) bus. The device used is an On Semiconductor 24C32 equivalent. The Module serial EEPROM is intended to retain Module parameter information, including a module serial number. The Module serial EEPROM data structure conforms to the PICMG® EEEP Embedded EEPROM Specification.). The onboard 4MB SPI NOR flash is used as SPI boot media. The module will always boot up from the onboard SPI NOR flash first. The firmware in NOR flash will read the configuration from the boot selection and boot up the devices from that selected.

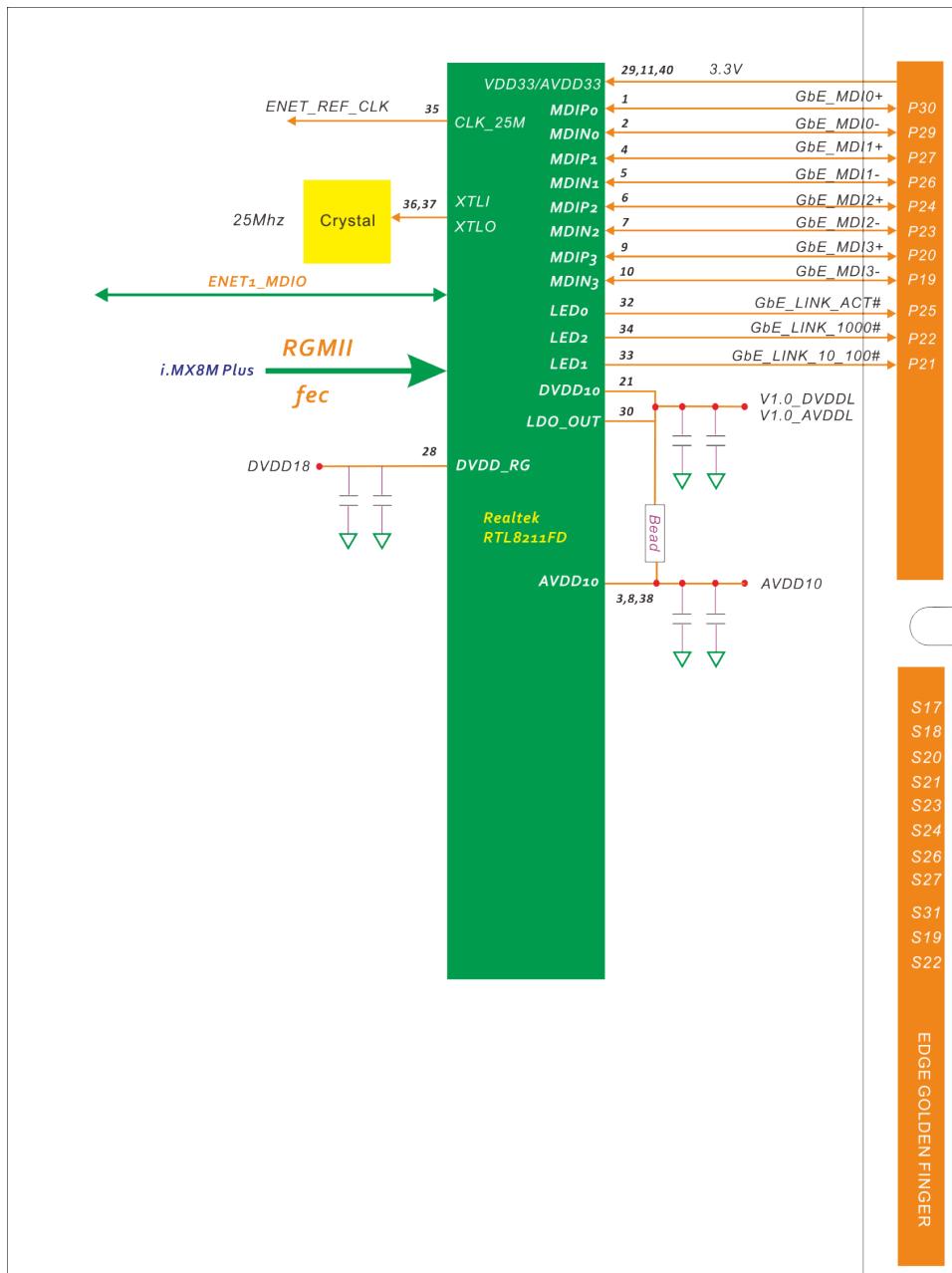

### 2.1.7. Clocks

A 32.768 KHz clock is required for the i.MX6 CPU RTC (Real Time Clock) and external (S-35390A) RTC.

The Freescale i.MX6 CPU is provided with a 24 MHz clock using a crystal in normal oscillation mode (On-chip Oscillator).

The Realtek RTL8211FD-CG Ethernet PHY is provided with a 24 MHz clock using a crystal in normal oscillation mode.

### 2.1.8. Multiple Displays with IPU in i.MX6

There are basically two limitations which have to be pointed out.

#### **IPU capabilities**

The two display ports (DI0 and DI1) of each IPU are limited to a combined pixel clock of 240MHz. The maximum clock for a single display port is 220MHz. This results in the following table (for one IPU only):

## Multiple Displays with IPU in i.MX6

| Second Display                             | SDTV<br>480i30 / 576i25<br>(27 MHz) | WSVGA<br>1024x600<br>(44 - 49 MHz) | HDTV<br>760p60 / 1080i30<br>(74.25 MHz) | WXGA<br>1366x768<br>(72 - 85 MHz) | WSXGA+<br>1680x1050<br>(119 - 146 MHz) | HDTV<br>1080p60<br>(148.5 MHz) |

|--------------------------------------------|-------------------------------------|------------------------------------|-----------------------------------------|-----------------------------------|----------------------------------------|--------------------------------|

| First Display                              |                                     |                                    |                                         |                                   |                                        |                                |

| <b>WXGA</b><br>1366x768 (72 - 85 MHz)      | Full                                | Full                               | Full                                    | Full                              | Full                                   | Full                           |

| <b>SXGA</b><br>1280x1024 (91 - 109 MHz)    | Full                                | Full                               | Full                                    | Full                              | Partial                                | Partial                        |

| <b>SXGA+</b><br>1400x1050 (101 - 124 MHz)  | Full                                | Full                               | Full                                    | Full                              | Partial                                |                                |

| <b>WSXGA+</b><br>1680x1050 (119 - 146 MHz) | Full                                | Full                               | Full                                    | Full                              | Partial                                |                                |

| <b>UXGA</b><br>1600x1200 (130 - 161 MHz)   | Full                                | Full                               | Full                                    | Partial                           |                                        |                                |

| <b>WUXGA</b><br>1920x1200 (154 - 191 MHz)  | Full                                | Partial                            | Partial                                 |                                   |                                        |                                |

| <b>9VGA</b><br>1920x1440 (185 - 234 MHz)*  | Partial                             | Partial                            |                                         |                                   |                                        |                                |

| <b>4XGA</b><br>2048x1536 (209 - 267 MHz)*  | Partial                             |                                    |                                         |                                   |                                        |                                |

- The table indicates the performance per IPU. Two IPUs are available in the dual- and quad-core versions of i.MX6.

- For a TV, the clock rate is fixed by the corresponding standards.

- The assumed screen refresh rate for other displays is 60 Hz.

- Resolutions marked with \* are not possible by LVDS.

- **Full** = allowing full blanking which is typical required for CRTs

- **Partial** = allowing only reduced blanking, which is still typical sufficient for digital displays, e.g. LCDs

The table above only describes the capabilities of the display ports to perform screen refresh. A full use case typically includes additional activities like video processing, resizing etc., decreasing the possible display resolutions.

### LVDS Serialization

Another limitation by using the LVDS interfaces is the maximum clock of the LVDS serializer. For single-channel output the pixel clock is limited to 85 MHz per LVDS port. This results in a maximum resolution of WXGA (1366x768 @ 60Hz with 35% blanking), for example. If a higher resolution is needed, the split mode has to be used. In this case one LVDS port outputs ODD data and the other port EVEN data. The pixel clock is limited to 170 MHz (e.g. UXGA 1600x1200 @ 60 Hz with 35% blanking). To use the split mode, you need a display supporting the dual channel LVDS mode in order to receive odd and even pixel data!

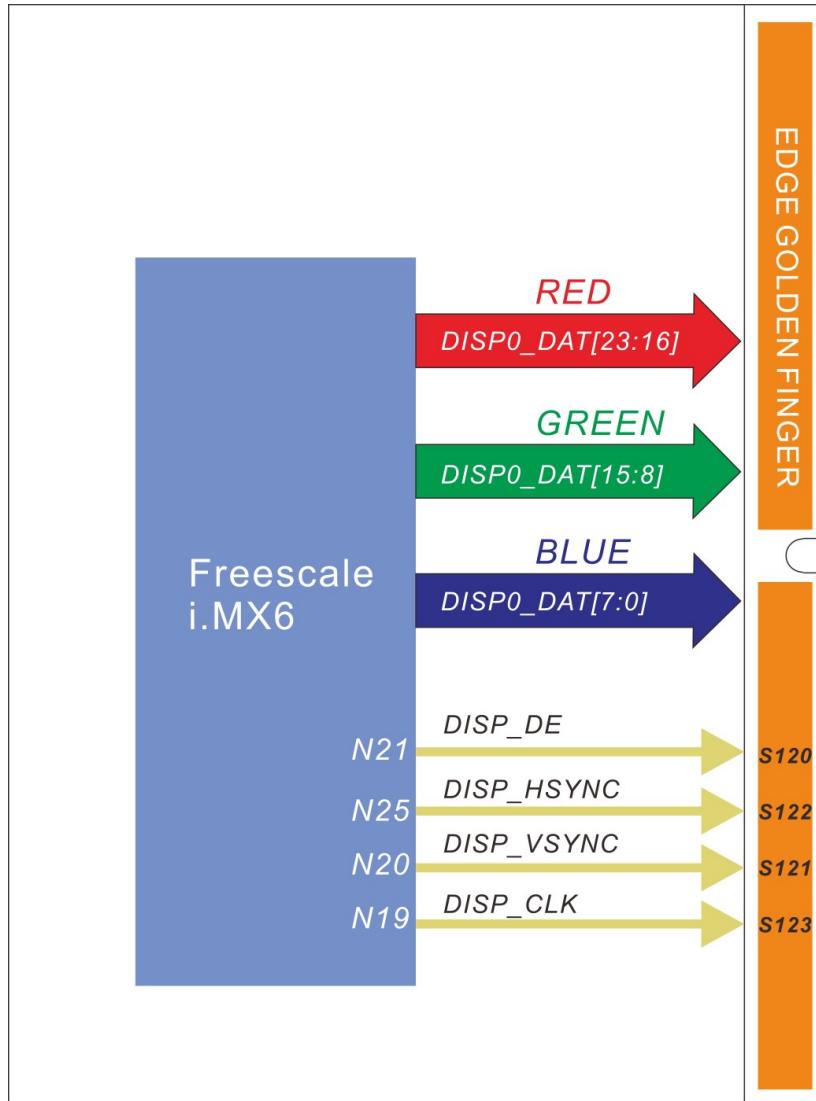

### 2.1.9. Parallel LCD Interface

The Freescale i.MX6 parallel 24 bit LCD interface is brought to the Module edge connector. The interface runs at the 3.3V or 1.8V Module I/O voltage depending on the part number that users select. The SMARC Module parallel LCD pins may be used to drive a traditional parallel LCD interface (or they may be used to drive LVDS transmitters or other transmitters that accept parallel LCD data at the Module VDD\_IO level).

For parallel displays with very small form factors (think cell phone and digital camera size), the data I/O level is usually 1.8V. For larger displays, the display will likely require a 3.3V data I/O level.

If the SMARC modules are with 3.3V VDD\_IO and parallel displays are with 3.3 V I/O, the SMARC Parallel LCD data signals may be passed directly to the display, for short cable runs. This voltage swing may be used directly with 3.3V capable Carrier Board LVDS transmitters, such as the TI SN75LVDS83B. The 3.3V signaling is suitable for direct connection to a parallel flat panel in most cases. Generally speaking, larger parallel LCD panels are likely to use 3.3V or 5V signaling. If LCD panels use 5V signaling, a set of voltage translators / buffers would be needed on the Carrier.

If the SMARC modules are with 1.8V VDD\_IO and parallel displays are with 1.8V I/O, the SMARC Parallel LCD data signals may be passed directly to the display, for short cable runs. For larger displays with 3.3V I/O level and the SMARC modules are 1.8V VDD\_IO, a bus transceiver like TI SN74AVC32T245-ZKE is required to achieve signal buffering and voltage translation from VDD\_IO to a 3.3V display. If there is a requirement for a display cable longer than a few inches, it may be a good idea to include the buffer even if the display accepts 1.8V I/O. The voltage swing may be used directly with 1.8V capable Carrier Board LVDS transmitters, such as TI DS90C185.

The following figure shows the parallel LCD block diagram.

**Figure 2: SMARC-FiMX6 Parallel LCD Diagram**

The mapping of the *Freescale i.MX6* parallel LCD pins to the SMARC edge connector is shown in the table below. Basically, *Freescale i.MX6* processor maps the 18 bits of R, G, B for 6 bit color depth to *DISP0\_DAT[23:18]*, *DISP0\_DAT[15:10]* and *DISP0\_DAT[7:2]*. For *i.MX6*, the extra bits used for a 24 bit color implementation come out on *Freescale i.MX6* *DISP0\_DAT[17:16]*, *DISP0\_DAT[9:8]* and *DISP0\_DAT[1:0]*. Since 18-bit configuration and 24-bit configuration use the same MSB signals, we can say 18-bit configuration is higher bits subset 24-bit configuration from the hardware point of view. The *SMARC* golden finger has the same convention: Red is *LCD\_D[23:16]*; Blue is *LCD\_D[15:8]* and Green is *LCD\_D[7:0]*. For 24 bit implementations, all bits are used. For 18 bit implementations, in *SMARC*, the least significant bits (Red *LCD\_D[17:16]*, Green *LCD\_D[9:8]*, Blue *LCD\_D[1:0]*) are dropped.

| Freescale i.MX6 CPU |      |                                                 | SMARC-FiMX6 Edge Golden Finger |                         |                | Net Names (Carrier Board) | Color | 24-bit Color Map |

|---------------------|------|-------------------------------------------------|--------------------------------|-------------------------|----------------|---------------------------|-------|------------------|

| Ball                | Mode | Pin Name                                        | Pin#                           | Pin Name                |                |                           |       |                  |

| W24                 | ALT0 | <i>DISP0_DAT23_</i><br><i>IPU1_DISP0_DATA23</i> | S118                           | <i>LCD_D23</i><br>(MSB) | <i>LCD_D23</i> |                           | R7    |                  |

| V24                 | ALT0 | <i>DISP0_DAT22_</i><br><i>IPU1_DISP0_DATA22</i> | S117                           | <i>LCD_D22</i>          | <i>LCD_D22</i> |                           | R6    |                  |

| T20                 | ALT0 | <i>DISP0_DAT21_</i><br><i>IPU1_DISP0_DATA21</i> | S116                           | <i>LCD_D21</i>          | <i>LCD_D21</i> |                           | R5    |                  |

| U22                 | ALT0 | <i>DISP0_DAT20_</i><br><i>IPU1_DISP0_DATA20</i> | S115                           | <i>LCD_D20</i>          | <i>LCD_D20</i> |                           | R4    |                  |

| U23                 | ALT0 | <i>DISP0_DAT19_</i><br><i>IPU1_DISP0_DATA19</i> | S114                           | <i>LCD_D19</i>          | <i>LCD_D19</i> |                           | R3    |                  |

| V25                 | ALT0 | <i>DISP0_DAT18_</i><br><i>IPU1_DISP0_DATA18</i> | S113                           | <i>LCD_D18</i>          | <i>LCD_D18</i> |                           | R2    |                  |

| U24                 | ALT0 | <i>DISP0_DAT17_</i><br><i>IPU1_DISP0_DATA17</i> | S112                           | <i>LCD_D17</i>          | <i>LCD_D17</i> |                           | R1    |                  |

| T21                 | ALT0 | <i>DISP0_DAT16_</i><br><i>IPU1_DISP0_DATA16</i> | S111                           | <i>LCD_D16</i><br>(LSB) | <i>LCD_D16</i> |                           | R0    |                  |

| T22                 | ALT0 | <i>DISP0_DAT15_</i><br><i>IPU1_DISP0_DATA15</i> | S109                           | <i>LCD_D15</i><br>(MSB) | <i>LCD_D15</i> |                           | G7    |                  |

| U25                 | ALT0 | <i>DISP0_DAT14_</i><br><i>IPU1_DISP0_DATA14</i> | S108                           | <i>LCD_D14</i>          | <i>LCD_D14</i> |                           | G6    |                  |

| R20                 | ALT0 | <i>DISP0_DAT13_</i><br><i>IPU1_DISP0_DATA13</i> | S107                           | <i>LCD_D13</i>          | <i>LCD_D13</i> |                           | G5    |                  |

| T24                 | ALT0 | <i>DISP0_DAT12_</i><br><i>IPU1_DISP0_DATA12</i> | S106                           | <i>LCD_D12</i>          | <i>LCD_D12</i> |                           | G4    |                  |

| T23                 | ALT0 | <i>DISP0_DAT11_</i><br><i>IPU1_DISP0_DATA11</i> | S105                           | <i>LCD_D11</i>          | <i>LCD_D11</i> |                           | G3    |                  |

| R21                 | ALT0 | <i>DISP0_DAT10_</i><br><i>IPU1_DISP0_DATA10</i> | S104                           | <i>LCD_D10</i>          | <i>LCD_D10</i> |                           | G2    |                  |

| T25                 | ALT0 | <i>DISP0_DAT9_</i><br><i>IPU1_DISP0_DATA09</i>  | S103                           | <i>LCD_D9</i>           | <i>LCD_D9</i>  |                           | G1    |                  |

| R22                 | ALT0 | <i>DISP0_DAT8_</i><br><i>IPU1_DISP0_DATA08</i>  | S102                           | <i>LCD_D8</i> (LSB)     | <i>LCD_D8</i>  |                           | G0    |                  |

| Freescale i.MX6 CPU |      |                                                | SMARC-FiMX6 Edge Golden Finger |                     |               | Net Names (Carrier Board) | Color | 24-bit Color Map |

|---------------------|------|------------------------------------------------|--------------------------------|---------------------|---------------|---------------------------|-------|------------------|

| Ball                | Mode | Pin Name                                       | Pin#                           | Pin Name            |               |                           |       |                  |

| R24                 | ALT0 | <i>DISP0_DAT7_</i><br><i>IPU1_DISP0_DATA07</i> | S100                           | <i>LCD_D7 (MSB)</i> | <i>LCD_D7</i> | BLUE                      | B7    |                  |

| R23                 | ALT0 | <i>DISP0_DAT6_</i><br><i>IPU1_DISP0_DATA06</i> | S99                            | <i>LCD_D6</i>       | <i>LCD_D6</i> |                           | B6    |                  |

| R25                 | ALT0 | <i>DISP0_DAT5_</i><br><i>IPU1_DISP0_DATA05</i> | S98                            | <i>LCD_D5</i>       | <i>LCD_D5</i> |                           | B5    |                  |

| P20                 | ALT0 | <i>DISP0_DAT4_</i><br><i>IPU1_DISP0_DATA04</i> | S97                            | <i>LCD_D4</i>       | <i>LCD_D4</i> |                           | B4    |                  |

| P21                 | ALT0 | <i>DISP0_DAT3_</i><br><i>IPU1_DISP0_DATA03</i> | S96                            | <i>LCD_D3</i>       | <i>LCD_D3</i> |                           | B3    |                  |

| V23                 | ALT0 | <i>DISP0_DAT2_</i><br><i>IPU1_DISP0_DATA02</i> | S95                            | <i>LCD_D2</i>       | <i>LCD_D2</i> |                           | B2    |                  |

| P22                 | ALT0 | <i>DISP0_DAT1_</i><br><i>IPU1_DISP0_DATA01</i> | S94                            | <i>LCD_D1</i>       | <i>LCD_D1</i> |                           | B1    |                  |

| P24                 | ALT0 | <i>DISP0_DAT0_</i><br><i>IPU1_DISP0_DATA00</i> | S93                            | <i>LCD_D0 (LSB)</i> | <i>LCD_D0</i> |                           | B0    |                  |

| Freescale i.MX6 CPU |      |                                                  | SMARC-FiMX6 Edge Golden Finger |                     | Net Names (Carrier Board) | Color | 24-bit Color Map |

|---------------------|------|--------------------------------------------------|--------------------------------|---------------------|---------------------------|-------|------------------|

| Ball                | Mode | Pin Name                                         | Pin#                           | Pin Name            |                           |       |                  |

| N19                 | ALT0 | <i>DI0_DISP_CLK_</i><br><i>IPU1_DI0_DISP_CLK</i> | S123                           | <i>LCD_PCK</i>      | <i>LCD_PCK</i>            |       |                  |

| N21                 | ALT0 | <i>DI0_PIN15_</i><br><i>IPU1_DI0_PIN15</i>       | S120                           | <i>LCD_DE</i>       | <i>LCD_DE</i>             |       |                  |

| N25                 | ALT0 | <i>DI0_PIN2_</i><br><i>IPU1_DI0_PIN02</i>        | S122                           | <i>LCD_HS</i>       | <i>LCD_HS</i>             |       |                  |

| N20                 | ALT0 | <i>DI0_PIN3_</i><br><i>IPU1_DI0_PIN03</i>        | S121                           | <i>LCD_VS</i>       | <i>LCD_VS</i>             |       |                  |

| T5                  | ALT5 | <i>GPIO_0_</i><br><i>GPIO1_I000</i>              | S127                           | <i>LCD_BKLT_EN</i>  | <i>LCD_BKLT_EN</i>        |       |                  |

| T1                  | ALT5 | <i>GPIO_2_</i><br><i>GPIO1_I002</i>              | S133                           | <i>LCD_VDD_EN</i>   | <i>LCD_VDD_EN</i>         |       |                  |

| T4                  | ALT5 | <i>GPIO_1_</i><br><i>PWM2_OUT</i>                | S141                           | <i>LCD_BKLT_PWN</i> | <i>LCD_BKLT_PWM</i>       |       |                  |

To use displays which require fewer bits (e.g. 18 or 16 bit displays), simply do not connect the bottom n LSBs for each color, where n is the number of signals that are not required for a specific color. For instance, to connect an 18 bit display, R0, R1, G0, G1, B0 and B1 will remain unused, and R2, G2 and B2 become the LSBs for this configuration.

### 2.1.9.1 Parallel LCD Data

| Edge Golden<br>Finder<br>Signal Name | Direction | Type<br>Tolerance | Description                                                                                          |

|--------------------------------------|-----------|-------------------|------------------------------------------------------------------------------------------------------|

| <i>LCD_D[16:23]</i>                  | Output    | CMOS<br>VDD_IO    | 8 bit RED color data - 18 bit display implementations leave the two LS bits (D16, D17) not connected |

| <i>LCD_D[8:15]</i>                   | Output    | CMOS<br>VDD_IO    | 8 bit GRN color data - 18 bit display implementations leave the two LS bits (D8, D9) not connected   |

| <i>LCD_D[0:7]</i>                    | Output    | CMOS<br>VDD_IO    | 8 bit BLU color data - 18 bit display implementations leave the two LS bits (D0, D1) not connected   |

| <i>LCD_PCK</i>                       | Output    | CMOS<br>VDD_IO    | Pixel clock – display data transitions on the positive clock edge                                    |

| <i>LCD_DE</i>                        | Output    | CMOS<br>VDD_IO    | Display Enable – signal is high during the active display line; low otherwise                        |

| <i>LCD_HS</i>                        | Output    | CMOS<br>VDD_IO    | Horizontal Sync – high pulse indicates the start of a new horizontal display line                    |

| <i>LCD_VS</i>                        | Output    | CMOS<br>VDD_IO    | Vertical Synch – high pulse indicates the start of a new display frame                               |

### 2.1.9.2 Parallel LCD Display Support Signals

The signals in the table below support the Parallel LCD and LVDS LCD interfaces (as these are created from the same i.MX6 source).

| Edge Golden<br>Finder<br>Signal Name | Direction                  | Type<br>Tolerance            | Description                                         |

|--------------------------------------|----------------------------|------------------------------|-----------------------------------------------------|

| <i>LCD_VDD_EN</i>                    | <i>Output</i>              | <i>CMOS</i><br><i>VDD_IO</i> | <i>High enables panel VDD</i>                       |

| <i>LCD_BKLT_EN</i>                   | <i>Output</i>              | <i>CMOS</i><br><i>VDD_IO</i> | <i>High enables panel backlight</i>                 |

| <i>LCD_BKLT_PWM</i>                  | <i>Output</i>              | <i>CMOS</i><br><i>VDD_IO</i> | <i>Display backlight PWM control</i>                |

| <i>I2C_LCD_DAT</i>                   | <i>Bi-Dir</i><br><i>OD</i> | <i>CMOS</i><br><i>VDD_IO</i> | <i>I2C data – to read LCD display EDID EEPROMs</i>  |

| <i>I2C_LCD_CK</i>                    | <i>Output</i>              | <i>CMOS</i><br><i>VDD_IO</i> | <i>I2C clock – to read LCD display EDID EEPROMs</i> |

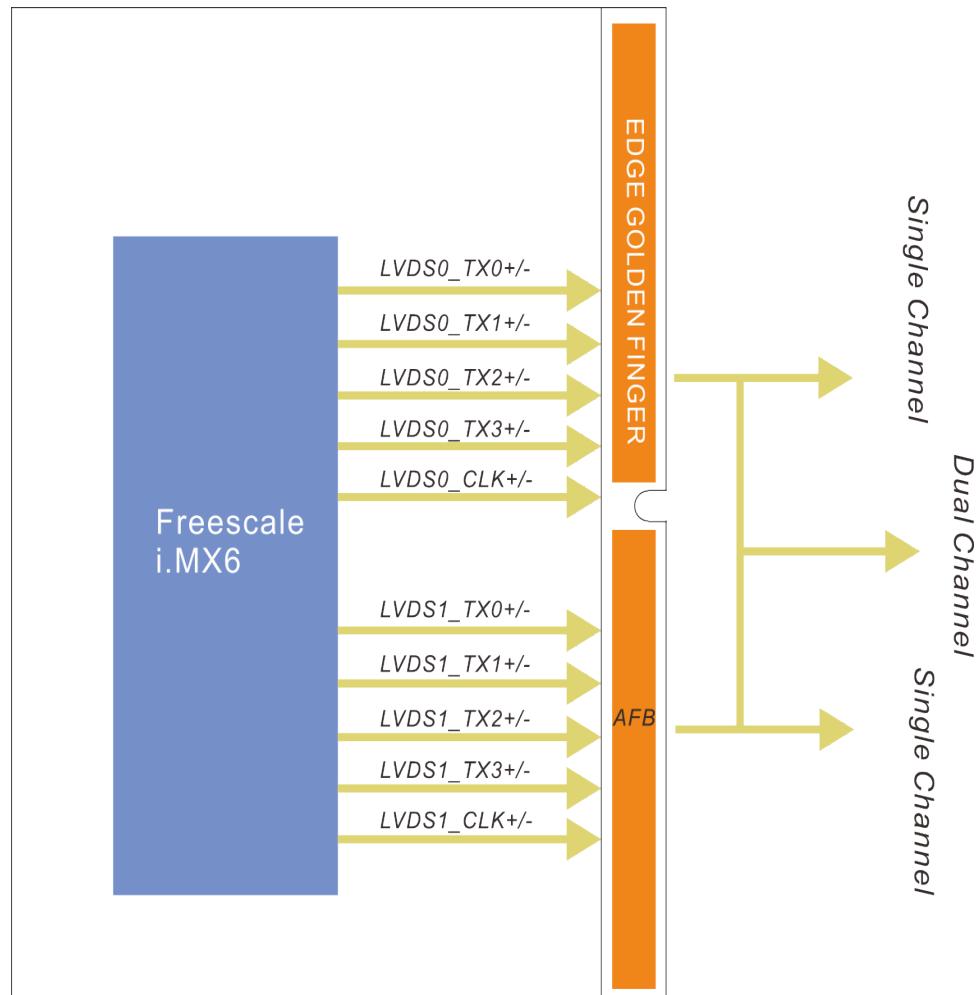

### 2.1.10 LVDS Interface

The SMARC-FiMX6 implements two 18 / 24 bit single channel LVDS output stream (the other LVDS is defined on AFB) for the Primary displays. They can also be configured as an 18 / 24 bit dual channel LVDS directly out of the SMARC Module.

The LVDS Display Bridge (LDB) from the Freescale® i.MX6 Cortex A9 processor found on the SMARC-FiMX6 offers two LVDS channels, with up to 170 Mhz pixel clock. Each channel consists of one clock pair and four data pairs. The LDB supports the flow of synchronous RGB data from the Image Processing Unit (IPU) to external display devices through LVDS interface.

The LVDS interface also supports various resolutions but with stipulated maximum data rates. The data rates supported are as follows:

For single channel output: Up to 85 MHz per interface (e.g 1366x768 @ 60 Hz + 35 % blanking).

For dual channel output: Up to 170 MHz pixel clock (e.g 1600x1200 @ 60Hz + 35 % blanking)

The LVDS ports support the following configurations:

- One single channel output

- One dual channel output: single input split to two output channels

- Two identical outputs: single input sent to both output channels

- Two independent outputs: two inputs sent, each to a different output channel

**Note:**

The *LVDS* interface can be used either as a single channel or as a dual channel. It is also possible to use the *LVDS* interface as two independent single *LVDS* channels if the iMX.6 processor on SMARC module has two *IPUs*. To do this, it is recommended to configure the *LVDS* display in the bootloader. (See Embedian developer guides.)

Three independent displays are possible when connected as two single *LVDS* channel and one *HDMI* interface.

The following figure shows the *LVDS LCD* block diagram.

**Figure 3: SMARC-FiMX6 LVDS LCD Diagram**

| Freescale i.MX6 CPU   |      |             | SMARC-FiMX6 Edge<br>Golden Finger |            | Net Names  | Note                                        |

|-----------------------|------|-------------|-----------------------------------|------------|------------|---------------------------------------------|

| Ball                  | Mode | Pin Name    | Pin#                              | Pin Name   |            |                                             |

| <b>LVDS Channel 0</b> |      |             |                                   |            |            |                                             |

| U1                    | ALT0 | LVDS0_TX0_P | S125                              | LVDS0+     | LVDS0_D0+  | LVDS0 LCD data channel differential pairs 1 |

| U2                    | ALT0 | LVDS0_TX0_N | S126                              | LVDS0-     | LVDS0_D0-  |                                             |

| U3                    | ALT0 | LVDS0_TX1_P | S128                              | LVDS1+     | LVDS0_D1+  | LVDS0 LCD data channel differential pairs 2 |

| U4                    | ALT0 | LVDS0_TX1_N | S129                              | LVDS1-     | LVDS0_D1-  |                                             |

| V1                    | ALT0 | LVDS0_TX2_P | S131                              | LVDS2+     | LVDS0_D2+  | LVDS0 LCD data channel differential pairs 3 |

| V2                    | ALT0 | LVDS0_TX2_N | S132                              | LVDS2-     | LVDS0_D2-  |                                             |

| W1                    | ALT0 | LVDS0_TX3_P | S137                              | LVDS3+     | LVDS0_D3+  | LVDS0 LCD data channel differential pairs 4 |

| W2                    | ALT0 | LVDS0_TX3_N | S138                              | LVDS3-     | LVDS0_D3-  |                                             |

| V3                    | ALT0 | LVDS0_CLK_P | S134                              | LVDS_CLK+  | LVDS0_CLK+ | LVDS0 LCD differential clock pairs          |

| V4                    | ALT0 | LVDS0_CLK_N | S135                              | LVDS_CLK-  | LVDS0_CLK- |                                             |

| <b>LVDS Channel 1</b> |      |             |                                   |            |            |                                             |

| Y2                    | ALT0 | LVDS1_TX0_P | S62                               | AFB_DIFF0+ | AFB_DIFF0+ | LVDS1 LCD data channel differential pairs 1 |

| Y1                    | ALT0 | LVDS1_TX0_N | S63                               | AFB_DIFF0- | AFB_DIFF0- |                                             |

| AA1                   | ALT0 | LVDS1_TX1_P | S65                               | AFB_DIFF1+ | AFB_DIFF1+ | LVDS1 LCD data channel differential pairs 2 |

| AA2                   | ALT0 | LVDS1_TX1_N | S66                               | AFB_DIFF1- | AFB_DIFF1- |                                             |

| AB2                   | ALT0 | LVDS1_TX2_P | S68                               | AFB_DIFF2+ | AFB_DIFF2+ | LVDS1 LCD data channel differential pairs 3 |

| AB1                   | ALT0 | LVDS1_TX2_N | S69                               | AFB_DIFF2- | AFB_DIFF2- |                                             |

| AA4                   | ALT0 | LVDS1_TX3_P | S74                               | AFB_DIFF4+ | AFB_DIFF4+ | LVDS1 LCD data channel differential pairs 4 |

| AA3                   | ALT0 | LVDS1_TX3_N | S75                               | AFB_DIFF4- | AFB_DIFF4- |                                             |

| Y4                    | ALT0 | LVDS1_CLK_P | S71                               | AFB_DIFF3+ | AFB_DIFF3+ | LVDS1 LCD differential clock pairs          |

| Y3                    | ALT0 | LVDS1_CLK_N | S72                               | AFB_DIFF3- | AFB_DIFF3- |                                             |

A 24 bit dual channel LVDS implementation comprises 10 differential pairs: 4 pairs for odd pixel and control data; 1 pair for the LVDS clock for the odd data; 4 pairs for the even pixel data and control data, and 1 pair for the even LVDS clock. To use the dual channel LVDS mode, you need a display supporting the dual channel LVDS mode in order to receive odd and even pixel data.

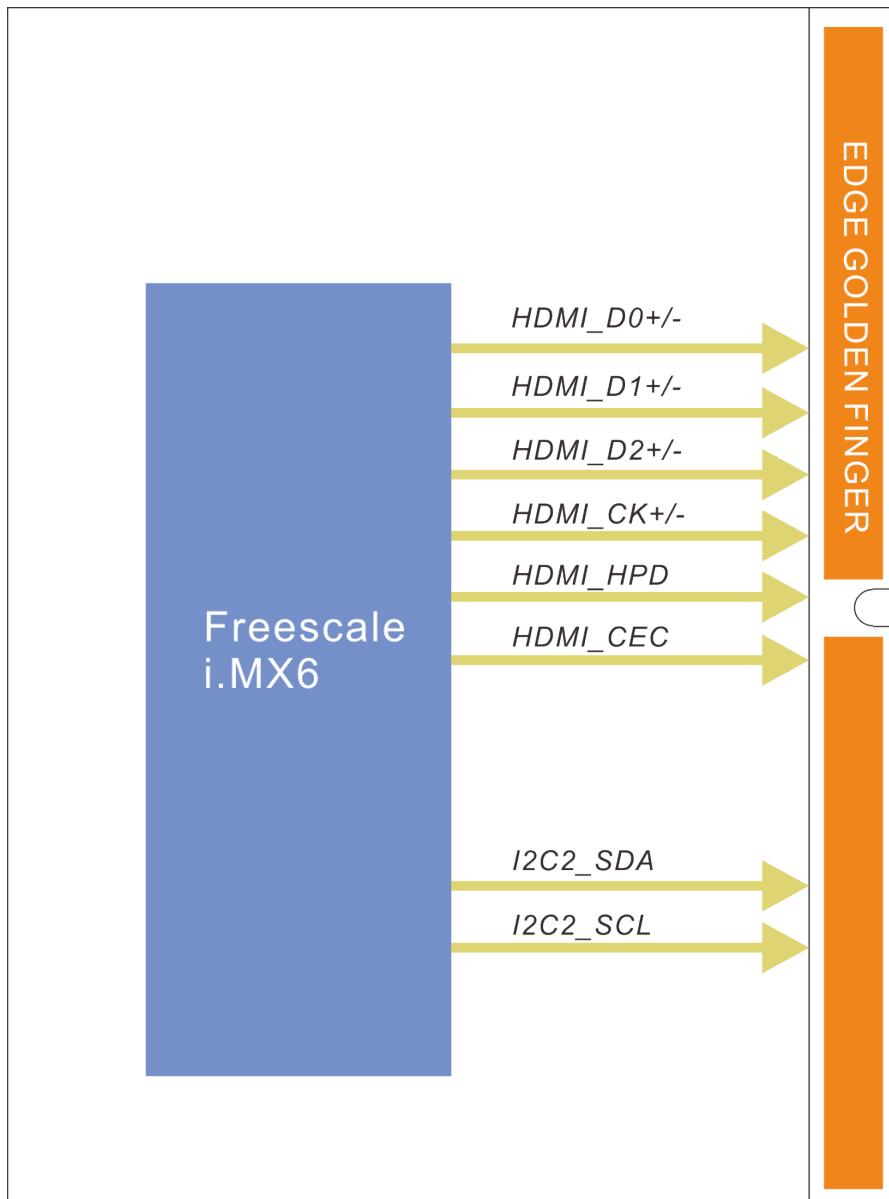

### **2.1.11. HDMI Interface**

High-Definition Multimedia Interface (HDMI) is a licensable compact audio/video connector interface for transmitting uncompressed digital streams. HDMI encodes the video data into TMDS for digital transmission and is backward-compatible with the single-link Digital Visual Interface (DVI) carrying digital video.

The SMARC-FiMX6 provides *HDMI* connection directly from the *Freescale® i.MX6* processor. Video data is provided through three differential TMDS data pairs (*HDMI\_D0±* to *HDMI\_D2±*) and one differential clock pair (*HDMI\_CLK±*). In addition, the SMARC-FiMX6 includes one standard I2C interface (*HDMI\_CTRL\_SDA* and *HDMI\_CTRL\_SCL*) for configuring and testing the HDMI 3D Tx PHY and a pin (*HDMI\_HPD*) for HDMI hot plug detection support.

The following figure shows the HDMI block diagram.

*Figure 4: SMARC-FiMX6 HDMI Diagram*

| Freescale i.MX6 CPU          |      |                   | SMARC-FiMX6<br>Edge Golden Finger |               | Net Names     |           | Note                                                                    |

|------------------------------|------|-------------------|-----------------------------------|---------------|---------------|-----------|-------------------------------------------------------------------------|

| Ball                         | Mode | Pin Name          | Pin#                              | Pin Name      |               |           |                                                                         |

| <b>HDMI</b>                  |      |                   |                                   |               |               |           |                                                                         |

| K5                           | N/A  | HDMI_D0M          | P99                               | HDMI_D0-      | HDMI_D0-      |           | TMDS / HDMI data differential pair 0                                    |

| K6                           | N/A  | HDMI_D0P          | P98                               | HDMI_D0+      | HDMI_D0+      |           |                                                                         |

| J3                           | N/A  | HDMI_D1M          | P96                               | HDMI_D1-      | HDMI_D1-      |           | TMDS / HDMI data differential pair 1                                    |

| J4                           | N/A  | HDMI_D1P          | P95                               | HDMI_D1+      | HDMI_D1+      |           |                                                                         |

| K3                           | N/A  | HDMI_D2M          | P93                               | HDMI_D2-      | HDMI_D2-      |           | TMDS / HDMI data differential pair 2                                    |

| K4                           | N/A  | HDMI_D2P          | P92                               | HDMI_D2+      | HDMI_D2+      |           |                                                                         |

| J5                           | N/A  | HDMI_CLKM         | P102                              | HDMI_CK-      | HDMI_CK-      |           | HDMI differential clock output pair                                     |

| J6                           | N/A  | HDMI_CLKP         | P101                              | HDMI_CK+      | HDMI_CK+      |           |                                                                         |

| K1                           | N/A  | HDMI_HPD          | P104                              | HDMI_HPD      | HDMI_HPD      |           | HDMI Hot Plug Detect input                                              |

| K2                           | N/A  | HDMI_DDCCEC       | P107                              | HDMI_CEC      | HDMI_CEC      |           | HDMI Consumer Electronics Control 1 – wire peripheral control interface |

| <b>I2C Dedicate for HDMI</b> |      |                   |                                   |               |               |           |                                                                         |

| T7                           | ALT4 | KEY_ROW3_I2C2_SDA | P106                              | HDMI_CTRL_DAT | HDMI_CTRL_DAT | I2C Data  |                                                                         |

| U5                           | ALT4 | KEY_COL3_I2C2_SCL | P105                              | HDMI_CTRL_CLK | HDMI_CTRL_CLK | I2C Clock |                                                                         |

### 2.1.11.1 HDMI Signals

The table below shows the HDMI related signals.

| <b>Edge Golden<br/>Finder<br/>Signal Name</b> | <b>Direction</b> | <b>Type<br/>Tolerance</b> | <b>Description</b>                           |

|-----------------------------------------------|------------------|---------------------------|----------------------------------------------|

| <i>HDMI_D[0:2]+</i>                           | <i>Output</i>    | <i>TDMS</i>               | <i>TMDS / HDMI data differential pairs</i>   |

| <i>HDMI_D[0:2]-</i>                           |                  |                           |                                              |

| <i>HDMI_CK+</i>                               | <i>Output</i>    | <i>TDMS</i>               | <i>HDMI differential clock output pair</i>   |

| <i>HDMI_CK-</i>                               |                  |                           |                                              |

| <i>HDMI_HPD</i>                               | <i>Input</i>     | <i>CMOS</i>               | <i>HDMI Hot Plug Detect input</i>            |

|                                               |                  | <i>VDD_IO</i>             |                                              |

| <i>HDMI_CTRL_DAT</i>                          | <i>Bi-Dir</i>    | <i>CMOS</i>               | <i>I2C data line dedicated to HDMI</i>       |

|                                               | <i>OD</i>        | <i>VDD_IO</i>             |                                              |

| <i>HDMI_CTRL_CK</i>                           | <i>Bi-Dir</i>    | <i>CMOS</i>               | <i>I2C clock line dedicated to HDMI</i>      |

|                                               | <i>OD</i>        | <i>VDD_IO</i>             |                                              |

| <i>HDMI_CEC</i>                               | <i>Bi-Dir</i>    | <i>CMOS</i>               | <i>HDMI Consumer Electronics Control</i>     |

|                                               |                  | <i>VDD_IO</i>             | <i>1 – wire peripheral control interface</i> |

HDMI displays uses 5V I2C signaling. The Module *HDMI\_CTRL\_DAT* and *HDMI\_CTRL\_CK* signals need to be level translated on the Carrier from the Module *VDD\_IO* level (3.3V or 1.8V). A similar consideration applies to the *HDMI\_HPD* signal. There are a number of single chip devices on the market that perform ESD protection and control signal level shifting for HDMI interfaces. The Texas Instruments *TPD12S016* is one such device.

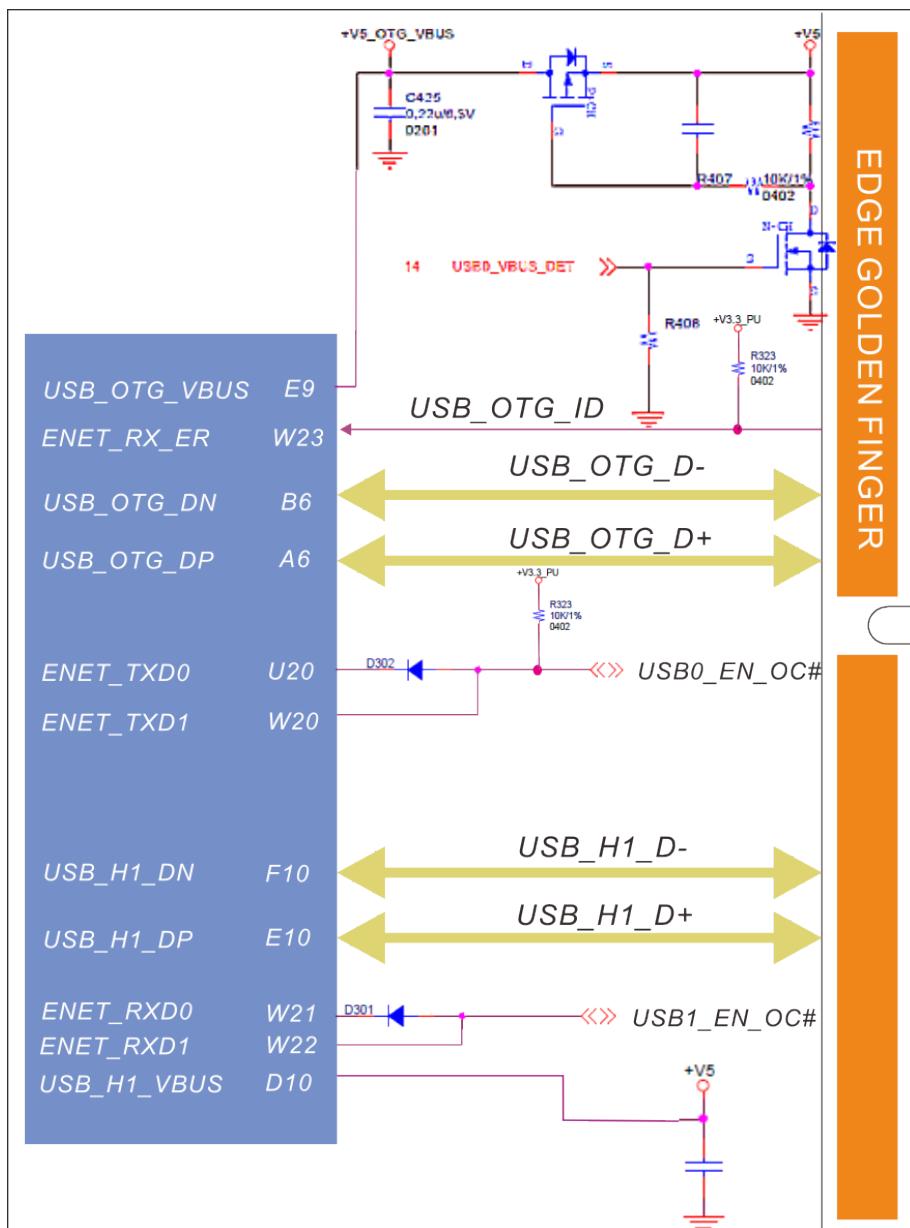

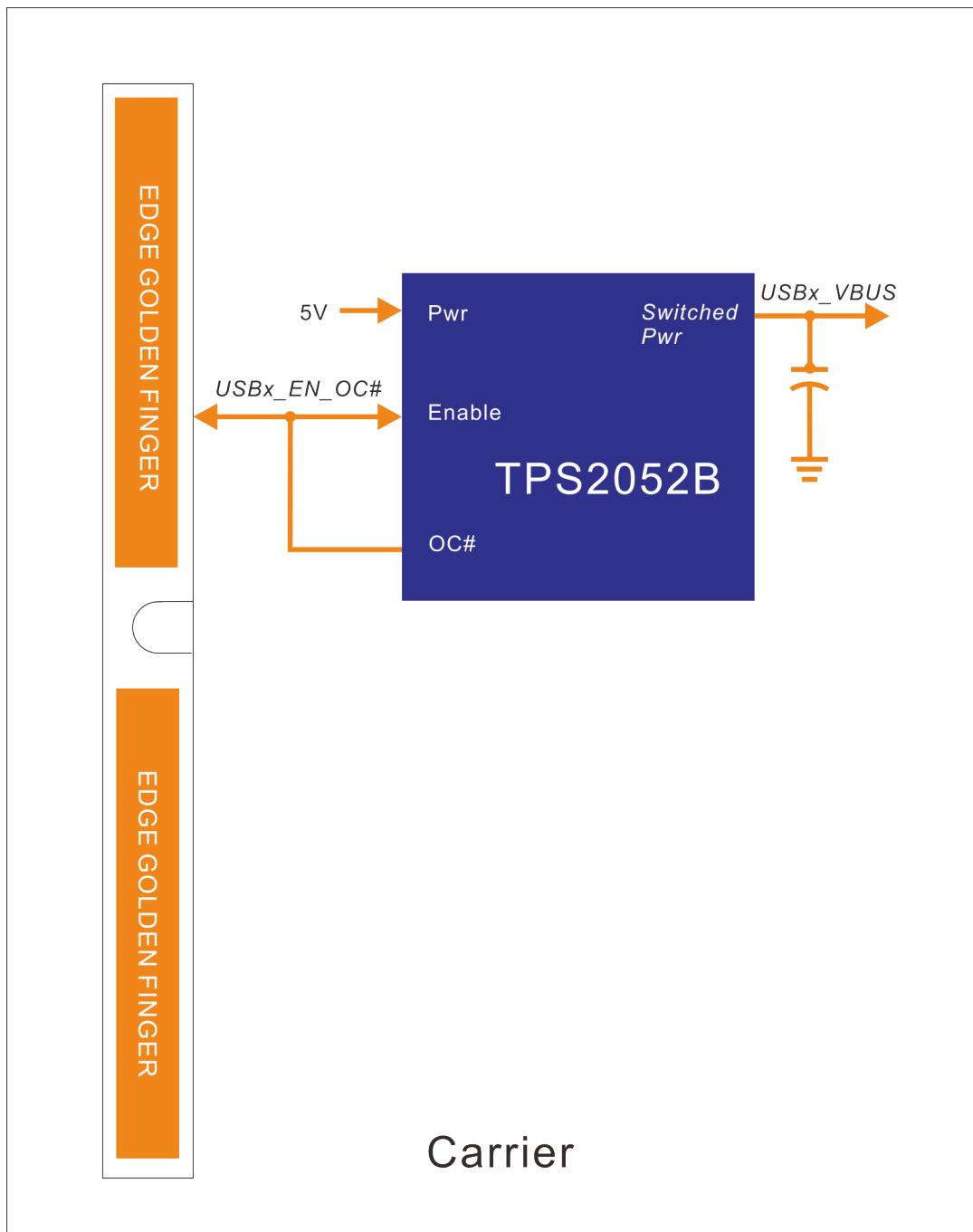

### 2.1.12 USB Interface

The Embeidian SMARC-FiMX6 module supports two USB ports (*USB 0:1*). Per the SMARC specification, the module supports a USB “On-The-Go” (OTG) port capable of functioning either as a client or host device, on the SMARC USB0 port. The SMARC-FiMX6 module also supports one additional USB2.0 host ports, on SMARC USB1.

The following figure shows the USB0 and USB1 block diagram.

**Figure 5. USB0 and USB1 Block Diagram**

USB interface signals are exposed on the SMARC-FiMX6 edge connector as shown below:

| <b>Freescale i.MX6 CPU</b>  |             |                                         | <b>SMARC-FiMX6 Edge Golden Finger</b> |                      | <b>Net Names</b>     | <b>Note</b>                                                          |

|-----------------------------|-------------|-----------------------------------------|---------------------------------------|----------------------|----------------------|----------------------------------------------------------------------|

| <b>Ball</b>                 | <b>Mode</b> | <b>Pin Name</b>                         | <b>Pin#</b>                           | <b>Pin Name</b>      |                      |                                                                      |

| <b>USB0 Port (OTG)</b>      |             |                                         |                                       |                      |                      |                                                                      |

|                             |             | <i>USB_OTG_DP</i>                       | P60                                   | <i>USB0+</i>         | <i>USB0+</i>         | <i>USB0 port data pair</i>                                           |

|                             |             | <i>USB_OTG_DN</i>                       | P61                                   | <i>USB0-</i>         | <i>USB0-</i>         |                                                                      |

| U20                         | ALT5        | <i>ENET_RXD0_</i><br><i>GPIO1_IO30</i>  | P62                                   | <i>USB0_EN_OC#</i>   | <i>USB0_EN_OC#</i>   | <i>USB Port0 power enable/over current indication signal</i>         |

| W20                         | ALT5        | <i>ENET_RXD1_</i><br><i>GPIO1_IO29</i>  |                                       |                      |                      |                                                                      |

| E9                          |             | <i>Turn on USB_OTG_VBUS</i>             | P63                                   | <i>USB0_VBUS_DET</i> | <i>USB0_VBUS_DET</i> | <i>USB host power detection, when this port is used as a device.</i> |

| W23                         | ALT0        | <i>ENET_RX_ER_</i><br><i>USB_OTG_ID</i> | P64                                   | <i>USB0_OTG_ID</i>   | <i>USB0_OTG_ID</i>   | <i>USB OTG ID input, active high</i>                                 |

| <b>USB1 Port (Host 2.0)</b> |             |                                         |                                       |                      |                      |                                                                      |

| E10                         |             | <i>USB_H1_DP</i>                        | P65                                   | <i>USB1+</i>         | <i>USB1+</i>         | <i>USB1 port data pair</i>                                           |

| F10                         |             | <i>USB_H1_DN</i>                        | P66                                   | <i>USB1-</i>         | <i>USB1-</i>         |                                                                      |

| W21                         | ALT5        | <i>ENET_RXD0_</i><br><i>GPIO1_IO27</i>  | P67                                   | <i>USB1_EN_OC#</i>   | <i>USB1_EN_OC#</i>   | <i>USB Port0 power enable/over current indication signal</i>         |

| W22                         | ALT5        | <i>ENET_RXD1_</i><br><i>GPIO1_IO26</i>  |                                       |                      |                      |                                                                      |

### 2.1.12.1 USB0 Signals

The table below shows the USB0 related signals.

| Edge Golden<br>Finder<br>Signal Name | Direction    | Type<br>Tolerance | Description                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|--------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB0+                                | Bi-Dir       | USB               | Differential USB0 Data Pair                                                                                                                                                                                                                                                                                                                                                |

| USB0-                                |              |                   |                                                                                                                                                                                                                                                                                                                                                                            |

| USB0_EN_OC#                          | Bi-Dir<br>OD | CMOS<br>3.3V      | <p>Pulled low by Module OD driver to disable USB0 power.</p> <p>Pulled low by Carrier OD driver to indicate over-current situation.</p> <p>A 10k pull-up is present on the Module to a 3.3V rail. The pull-up rail may be switched off to conserve power if the USB port is not in use. Further details may be found in Section 2.1.12.3 USBx_EN_OC# Discussion below.</p> |

| USB0_VBUS_DET                        | Input        | USB VBUS<br>5V    | USB host power detection, when this port is used as a device.                                                                                                                                                                                                                                                                                                              |

| USB0_OTG_ID                          | Input        | CMOS<br>3.3V      | USB OTG ID input, active high.                                                                                                                                                                                                                                                                                                                                             |

### 2.1.12.2 USB1 Signals

USB1 port is a USB 2.0 host port. The table below shows the USB1 related signals.

| Edge Golden<br>Finder<br>Signal Name | Direction                  | Type<br>Tolerance          | Description                                                                                                                                                                                                                                                                                                                                                                                            |